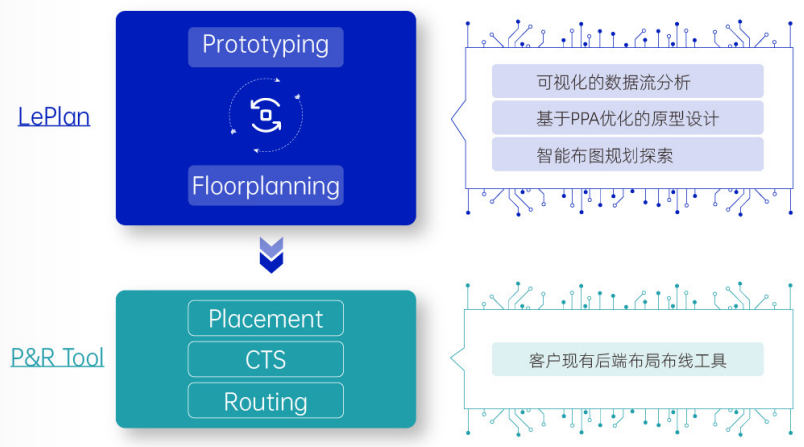

上海立芯软件科技有限公司(简称上海立芯)于近日发布一款已通过客户验证的数字集成电路自动化布图规划工具LePlan,为国产数字集成电路后端设计全流程EDA工具的破局助力。

长期以来,在数字芯片后端设计之首的布图规划(Floorplanning)阶段,数字设计主要依赖芯片设计人员的经验来摆放宏单元(macro)。随着集成电路设计规模的持续增大和宏单元个数迅速增长,手工布图规划很难妥善考虑对后续布局布线及面积、拥塞、时序、线长等性能指标的影响。其造成的结果就是耗费大量时间进行多次迭代,不仅增加芯片开发时间,也不能保证收敛。因此,在手工布图规划捉襟见肘之际,数字设计流程迫切需要以创新性的优化算法,寻求自动化工具解决这一现实问题。

LePlan图形界面

上海立芯董事长陈建利博士表示,“伴随着集成电路制程从成熟工艺向7nm以下制程不断演进,公司敏锐地针对于数字芯片设计在布图规划环节对自动化工具的迫切需求,快速推出经过验证且商用的自动化布图规划工具LePlan”。

LePlan的关键特征和亮点包括:

可视化的数据流分析 LePlan可以为用户提供清晰直观的数据流分析,来展示宏单元以及各子模块之间的连接关系;用户可分别以用线模式、时序模式以及多级时序模式,对设计中的关键时序路径做精细化分析,帮助用户在其设计中实现更优的性能指标。

混合尺寸布局 LePlan基于内嵌的数据流分析引擎,实现宏单元和标准单元的混合布局;基于创新的布局布线技术,具有对拥塞、线长、时序等进行精准预估以及计算的功能,以保证设计的可绕通性和时序可收敛性。

智能布图规划探索 LePlan基于机器学习的智能规划探索算法,针对拥塞、线长、时序、宏单元规整性等多个优化指标,通过不同阶段持续迭代出多种高质量布图规划方案,实现优中选优,用户可以根据设计目标快速选择其中的最优解。

宏单元自动对齐 LePlan支持先进工艺下宏单元布局的物理约束,可以实现宏单元之间的对齐以及背靠背功能;精准的电源网络绕线资源预估和拥塞计算功能还保证了宏单元之间的沟道可绕通性,极大地减少了用户对宏单元摆放的人工干预,从而加速设计迭代。

从客户的设计实例来看,LePlan较手工布图在整体上有明显的PPA优化优势,效率亦有显著提升。在某款先进工艺的CPU设计实例中,LePlan工具较手工布图分别实现TNS、标准单元面积、静态功耗各有88.7%、1.8%、7.2%的优化。在另一款先进工艺的Video设计实例中,TNS降低35.8%,标准单元面积减小0.6%,静态功耗减少5.8%。

上海立芯董事长陈建利博士表示,“LePlan工具针对性地破解传统手工布图规划难以解决的耗时和收敛性差等多方面难题,提供基于数据流分析和智能探索达到最快收敛的布图规划方案,旨在助力数字电路设计实现更具挑战性的PPA要求。特别地,LePlan还高度融合后端布局布线技术,同时降低集成风险。该工具后续将大规模推向市场,满足更多设计客户的需求”。