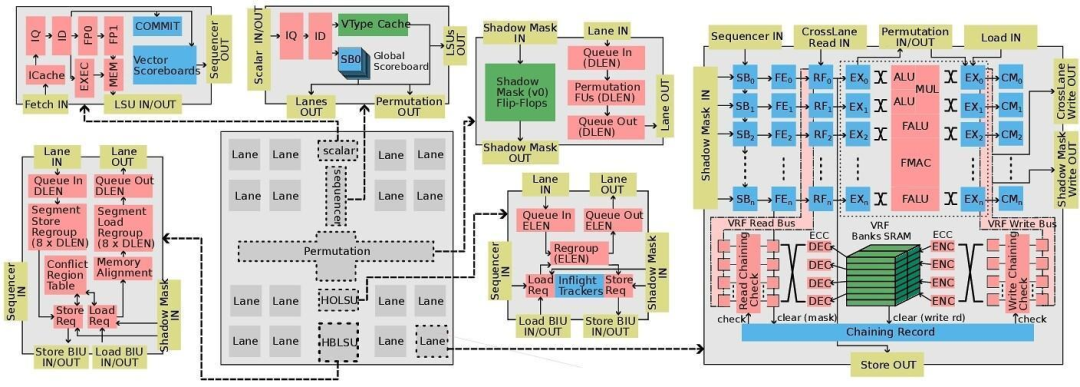

10月20日,集成电路学院邹雪城团队博士生刘玖阳的研究课题《高性能RISC-V向量核心》在体系结构领域取得重要突破,并被第58届计算机体系结构顶会MICRO接收并现场做报告。该项研究提出一款开源的、支持乱序执行的高性能RISC-V向量核“Titan-I”,解决现代计算中向量处理器的扩展性难题,为HPC和密码学等高算力需求领域提供了新的解决方案。论文题为《Titan-I: An Open-Source, High Performance RISC-V Vector Core》,论文第一作者为集成电路学院博士生刘玖阳,该项研究在 MICRO-58斩获全部三项“Artifact Evaluation”官方认证徽章。

传统向量架构在扩展数据路径宽度和向量长度时,面临严重的路由拥塞、掩码广播和指令级并行调度瓶颈,难以满足HPC和密码学等工作负载的需求。为解决这些挑战,研究团队提出的T1架构引入了多项微体系结构创新。在数据并行方面,采用粗粒度布局规划求解器、全带宽置换单元和掩码寄存器缓存,有效突破了物理布线和数据广播瓶颈。在指令级并行方面,通过细粒度链接、内存交错和基于记分板的向量-标量OoO(乱序执行)调度技术,极大提升了执行效率和资源利用率。

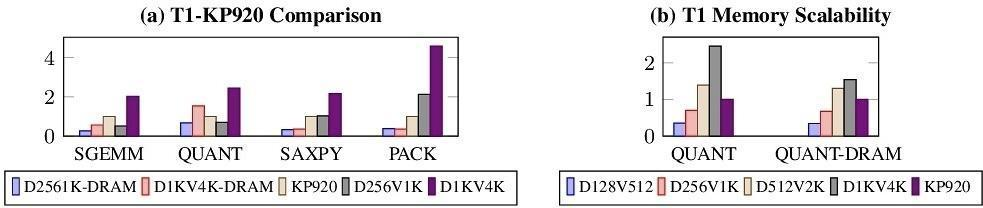

T1的性能表现卓越,在HPC方面,与海思鲲鹏KP920相比,T1仅用19%的面积即实现可比性能;

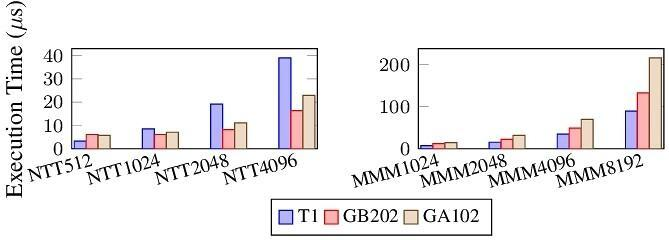

在密码学方面,与NVIDIA 3090相比,T1仅用40%的SM面积,实现了高达2.41倍的性能提升。

该研究为高性能RISC-V向量架构提供了新的平台与工程路线,有望加速其在RISC-V HPC,AI,后量子密码学中的落地应用。该研究是产学研协同创新的典范,项目通过Linux Foundation基金会的ChipsAlliance组织汇聚了来自华中科技大学、中国科学院、清华大学、浙江大学以及武汉心片科技有限公司等多家单位共同开源协作。T1架构已获客户导入,用于开发全同态加密加速器和边缘AI芯片。

论文第一作者刘玖阳博士,长期致力于硬件设计领域专用语言、形式化验证及计算机体系结构的研究。作为开源RISC-V处理器和EDA领域的知名技术专家,他曾深度参与SiFive CPU和SoC生成器的研发工作,同时也是RocketChip SoC平台的主要维护者和Chisel语言的核心开发者。