(集微网报道)引入AI技术是EDA行业近年来最大的变革之一,有望彻底改写芯片设计行业。近日,Cadence公司发布了基于机器学习(ML)的设计工具Cerebrus Intelligent Chip Explorer,将加速数字芯片设计流程的自动化进程。

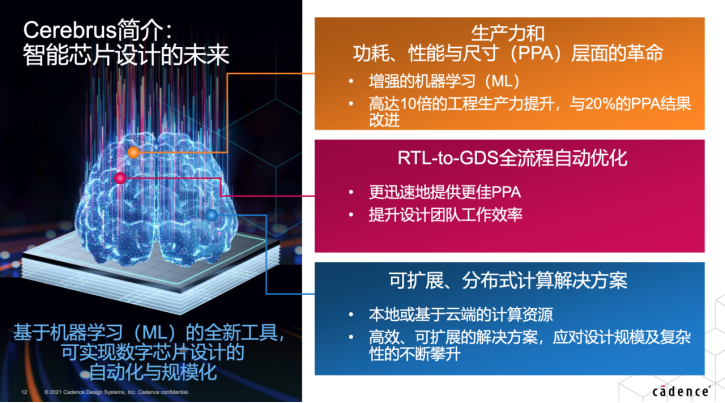

Cerebrus主要与Cadence RTL-to-signoff相结合,为高阶工艺芯片设计师、CAD 团队和 IP 开发者提供支持,与人工方法相比,将工程生产力提高多达 10 倍,同时最多可将功耗、 性能和面积 (PPA) 结果改善 20%。

据Cadence公司数字与签核事业部产品工程资深群总监刘淼介绍,除了提升工程生产力之外,这款工具还有两大亮点:一是会带来全新的自动化RTL to GDS流程,二是具有很大的扩展性,可以利用各种云资源来完成计算。

近年来,芯片的应用场景不断拓展,从消费电子、HPC、移动设备一直延伸到自动驾驶等领域,这就给芯片设计工程师带来一个重大的挑战,芯片开发进程要不断加快。Cerebrus诞生的意义就是为了让设计者能快速开发出高性能的芯片。

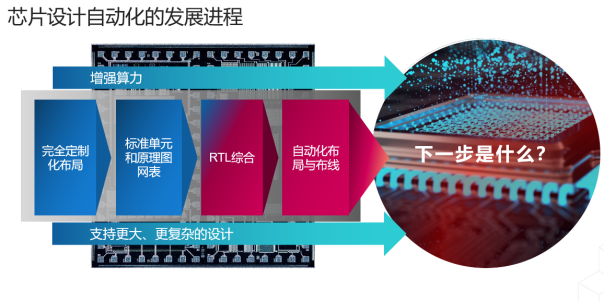

回看整个芯片设计自动化的过程,从完全定制化布局开始,随着EDA工具的不断增强,逐渐过渡至RTL综合,进而到自动化布局与布线。而随着机器学习时代的到来,Cerebrus这样的全新EDA工具终于诞生,来辅助工程师设计出性能更高、结构更复杂的芯片。

作为更广泛的 Cadence 数字全流程的一部分,Cerebrus可与 Genus Synthesis Solution 综 合解决方案、Innovus Implementation System 设计实现系统、Tempus Timing Signoff Solution 时序签核解决方案等相结合,大幅优化其中复杂的设计步骤。

“使用了Cerebrus,一个工程师用十天就可以改进5纳米CPU设计的PPA。”刘淼告诉集微网,“Cerebrus还可以帮助工程师做各种各样的探索,通过探索可以得到最优解,让芯片的性能大幅提升。”

他分享了一个应用案例,瑞萨的车规级芯片使用Cerebrus来做流程,一共模拟出400万种可能的流程,Cerebrus只跑了80个就实现了定位,给这个芯片带来性能10%的提升。

由于Cerebrus功能十分强大,有人担心会使得工程师面临失业困境,刘淼认为这种担心是多余的,“首先,Cerebrus要基于人的经验去学习,所以离不开人;第二,Cerebrus主要完成80%的工作,而还有20%更加有价值的工业还是要靠人去完成的。”

“我们是把你从那些比较繁琐的工作中解放出来,让你做可以有价值的工作,比如可以思考这个芯片如何堆叠,芯片的架构怎样走在最前面。”刘淼认为Cerebrus还可以解决芯片人才缺乏的问题,“最近中国半导体很火,带来的问题就是人才短缺,而Cerebrus可以引导缺乏经验的新人,很快解决在芯片设计中所面临的问题。”

对于Cerebrus给予工程人员的帮助,Cadence公司资深副总裁兼数字与签核事业部总经理 Chin-Chi Teng博士也表示,“Cerebrus 的面世标志着EDA行业迎来了一场颠覆性的革新,以机器学习为核心的数字芯片设计工具将让工程团队有更多机会在项目中发挥更大的影响力,因为他们可以告别重复性的手动流程。”

据刘淼介绍,对Cerebrus的改进还会继续进行,“首先要让现有的模型做得更加准,其次,未来可能会根据不同的芯片做一些模型,再根据工艺做一些模型,这些模型可以成为初始值,显著降低初始流程的数量,最终让Cerebrus的精准度变得更高。”(校对/Andrew)

登录

登录