2025年12月17日,南京大学集成电路学院王欣然、李卫胜团队与合作者创新开发出锑晶体外延接触技术,解决了亚20纳米接触长度下二维半导体欧姆接触难题,成功研制出1纳米节点高性能二硫化钼(MoS₂)晶体管器件,展示了二维半导体应用于埃米时代集成电路的潜力。相关成果以“Scaled crystalline antimony Ohmic contacts for two-dimensional transistors”为题,在线发表于《Nature Electronics》期刊。

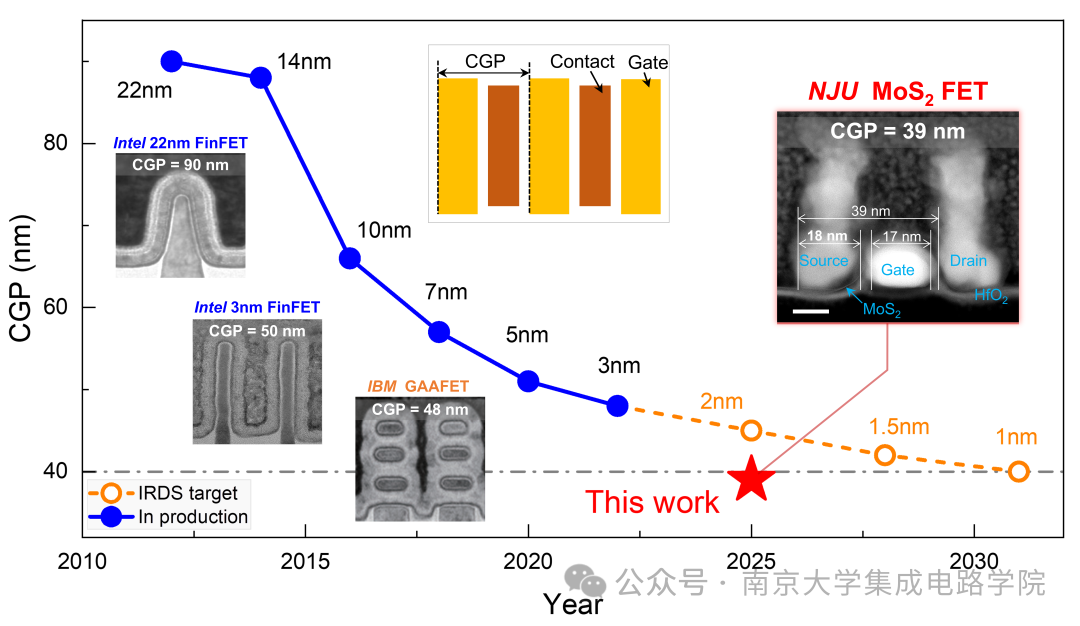

集成电路制程节点是由相邻晶体管的物理间距,即接触栅间距(CGP,包括栅长、接触长度与2倍栅源间隔长度)定义的。在摩尔定律的驱动下,过去60年晶体管器件的CGP持续微缩,例如45纳米节点平面FET的CGP定义为160纳米,英特尔22纳米节点FinFET的CGP定义为90纳米,而目前最先进的量产工艺台积电3纳米节点FinFET的CGP定义为48纳米。根据国际器件与系统路线图(IRDS),1纳米节点晶体管CGP将微缩至40纳米,已达到硅基器件的物理极限。

二维半导体材料因其原子级厚度和优异的微缩潜力,被公认为后摩尔集成电路最具希望的非硅新材料,受到全球学术界和产业界的高度关注。近年来,二维半导体晶体管研究取得了显著进展,但其接触长度和CGP通常维持在数百纳米以上,难以满足先进制程对器件尺寸的严格要求。实现CGP的深度微缩,关键在于构建具备超短载流子注入长度(即传输长度)和极低接触电阻的欧姆接触。IRDS要求1纳米节点晶体管的接触长度缩减至20纳米以下,同时接触电阻低于116 Ω·μm。当前的技术虽然能在微米级接触长度下实现低接触电阻,但当接触长度微缩至20纳米时,受电流拥挤效应影响,接触电阻呈指数级上升,成为制约二维半导体器件发展的核心瓶颈。

团队在前期原创提出的轨道杂化增强接触机制的基础上(Nature 613, 274 ( 2023)),在MoS₂上创新开发了分子束外延锑晶体(012)接触技术,首次在20纳米以下接触长度实现了小于100Ω·μm的接触电阻,满足了IRDS对1纳米节点晶体管的要求。分子束外延以其原子级精度控制能力和优异的界面质量,在构建高质量金属-半导体接触方面展现出无可比拟的优势。相比传统电子束蒸镀方法存在的相纯度低、晶畴尺寸受限等问题,分子束外延可实现几乎单一取向纯度(97.2%)的锑(012)晶体薄膜,晶畴尺寸提升两个数量级,并与MoS₂形成原子级锐利的界面。

基于深度微缩的锑晶体欧姆接触技术,团队成功研制出CGP小于40 纳米的高性能MoS₂晶体管器件。该晶体管的接触长度为18纳米,栅长为17纳米,在0.7V源漏偏压下具有1.08 mA/μm的高驱动电流,大于10⁷的开关比,小于10 pA/μm的关态电流,62 mV/dec的亚阈值斜率和12mV/V的漏致势垒降低,关键性能-功耗-尺寸(PPA)指标达到1纳米节点技术要求。TCAD器件仿真表明,锑晶体接触的传输长度为13纳米,可支撑MoS₂晶体管微缩至亚1纳米节点。晶圆级外延和晶体管阵列测试进一步证实了锑晶体接触的高均一性、可靠性和重复性。

该成果为集成电路走向埃米时代提供了方案。由南京大学、苏州实验室与华为等单位联合攻关完成,第一作者为南京大学—苏州实验室联合培养博士研究生杜明奕,通讯作者为李卫胜副教授和王欣然教授,南京大学施毅院士、香港中文大学许建斌教授对本工作进行了全程指导。研究得到了国家重点研发计划、国家自然科学基金、江苏省前沿技术研发计划、苏州创新创业领军人才等项目的资助,以及新基石科学基金会科学探索奖、雅辰基金、小米基金的支持。

图1 先进制程晶体管发展历程

图2 锑晶体接触的1纳米节点MoS₂晶体管