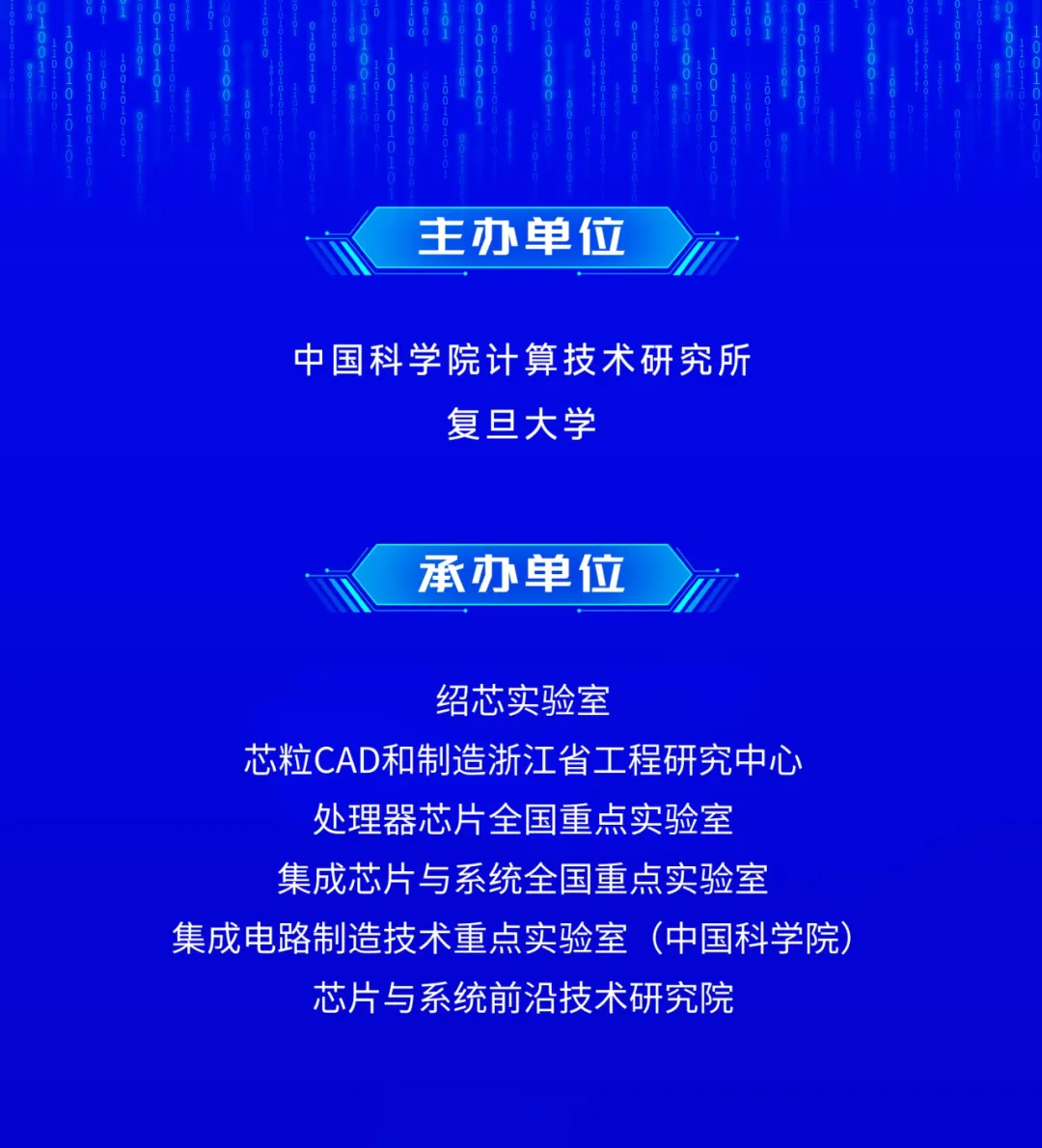

2024年11月8日-10日,以“集成芯片:迈进大芯片时代”为主题的第二届集成芯片和芯粒大会将在北京嘉里大酒店举行。本次大会由基金委集成芯片前沿科学基础重大研究计划指导专家组指导,由中国科学院计算技术研究所、复旦大学主办,目前会议注册通道已经开放,会议详细日程日程已经确定,正在火热报名中!

会议注册通道已经开放,火热报名中!

注册方式及费用

扫描下方二维码,或登录会议官方网站(https://2024.iccconf.cn/),点击“注册缴费”→提交信息→“我要缴费”。学生票价格为1000元(不含晚宴),非学生票价格为2000元。

更多会议酒店周边的住宿信息和预订方式可参考:https://2024.iccconf.cn/address

大会介绍

本次会议将以“集成芯片:迈进大芯片时代”为主题,探讨集成芯片与芯粒技术的前沿动态与未来发展趋势,包括集成芯片体系结构和电路设计、集成芯片数学基础和EDA、多物理场仿真、集成技术等热点议题。孙凝晖院士、刘明院士担任大会主席,中国科学院计算技术研究所韩银和研究员、复旦大学刘琦教授担任大会技术委员会主席。北京大学蔡一茂教授、武汉大学郭宇铮教授、中国科学院微电子研究所李泠研究员、国家数字交换系统工程技术研究中心刘勤让研究员、清华大学吴华强教授组成本次大会的技术委员会。

大会详细日程

本次大会将提供大量精彩报告,其具体日程如下。其中,11月8日,中国科学院院士彭练矛将做题目为“基于低维半导体的晶体管技术”的主旨报告,IEEE Fellow刘汉诚将做题目为“Advanced Substrates for Chiplets and Heterogeneous Integration”的主旨报告,中国电子信息产业集团首席科学家窦强将做题目为“集成大算力芯片的挑战与应对”的主旨报告。11月9日,中国科学院院士陈志明将做题目为“有限元方法最新进展”的主旨报告,清华大学集成电路学院院长吴华强将做题目为“Chiplet技术发展趋势及标准生态建设”的主题报告,赖梁祯博士将做主旨报告。复旦大学刘琦教授将组织Panel集体讨论。

另外,大会将在11月8日和11月9日分别组织5个分论坛,围绕集成芯片和芯粒技术的核心问题展开,涵盖从体系结构、仿真技术到供电架构与互连缩微等多个前沿领域。论坛话题紧扣行业发展趋势,将深入探讨当前集成芯片和芯粒技术中的关键难题与技术瓶颈,提供广泛的技术视角和创新思路。这些议题不仅回应业界的热点关切,还为未来技术突破指引方向,是推动集成芯片技术向前迈进的重要平台。

分论坛详细日程

论坛一 UCIe和国产芯粒互连标准技术进展

13:30 - 14:00 UCIe 2.0: 芯粒互连标准的演进和创新

阿里云 首席云服务架构师 陈健

14:00 - 14:30 芯粒互连标准融合的挑战与创新:国产TCESA 1248-2023与IEEE P3468

南京大学 杜源教授

14:30 - 15:00 芯粒间互联通信协议与“赛柏1号”桥接互联芯粒

电子科技大学 黄乐天教授

15:00 - 15:30 CMOS工艺兼容的Chiplet光互连接口芯片

中国科学院半导体研究所 祁楠研究员

15:30 - 15:50 茶歇

15:50 - 16:20 AIGC时代下的Chiplet互联趋势与D2D接口技术

奇异摩尔集成电路设计有限公司 高级设计经理 王彧

16:20 - 16:50 互连链路中快速建立与自测试技术

西安电子科技大学 赵潇腾教授

论坛二 布局布线EDA工具的三维化发展趋势

13:30 - 14:00集成芯片的架构探索和物理设计

芯粒CAD和制造浙江省工程研究中心 林廷容副研究员

14:00 - 14:30 三维集成电路的时钟树综合优化

上海科技大学 周平强研究员

14:30 - 15:00 面向PCB自动布局布线技术发展与挑战

武汉理工大学 徐宁教授

15:00 - 15:30 2.5D/3D FPGA设计挑战与应对

西南交通大学 邸志雄副教授

15:30 - 15:50 茶歇

15:50 - 16:20 Toward Advancing 3D-ICs Physical Design: Challenges and Opportunities

鹏城实验室 李兴权 副研究员

16:20 - 16:50 Physical Parameter Optimization in Advanced Packaging

复旦大学 朱可人青年研究员

论坛三 集成芯片的多物理场仿真难题

13:30 - 14:05 考虑芯粒集成工艺过程效应的集成芯片多物理场建模仿真方法集成芯片的架构探索和物理设计

浙江大学 陈文超研究员

14:05 - 14:40 毫米波三维异质异构集成电路与系统

上海交通大学 周亮教授

14:40 - 15:15 晶体管级电路仿真的硬件加速

华大九天 周振亚副总经理

15:15 - 15:35 茶歇

15:35 - 16:10 多芯粒封装中2.5D互连线仿真及优化

杭州电子科技大学 王高峰教授

16:10 - 16:45 面向大规模仿真问题的线性方程组迭代求解

清华大学 喻文健教授

16:45 - 17:20 AI加速多物理模型和左移设计

芯粒CAD和制造浙江省工程研究中心 吴晨助理研究员

论坛四 集成芯片供电架构及电源芯粒前沿技术

13:30 - 14:00 先进半导体封装与集成技术在电源模块中的应用

香港应用科技研究院 高级总监 高子阳

14:00 - 14:30 面向处理器的高密度电源管理技术研究

浙江大学 屈万园教授

14:30 - 15:00 高密度电容型集成电源芯片

南方科技大学 姜俊敏副教授

15:00 - 15:30 集成芯片中的低压降稳压器电路与模拟电路设计自动化

清华大学 刘效森副教授

15:30 - 15:50 茶歇

15:50 - 16:20 封装基板集成磁元件技术发展简介

杭州电子科技大学 王宁宁教授

16:20 - 16:50 面向多核处理器的分核供电技术研究

澳门大学 毛翔宇博士后

论坛五 顶会论坛-体系结构

13:30 - 13:55 ICGMM: CXL-enabled Memory Expansion with Intelligent Caching Using Gaussian Mixture Model 先进半导体封装与集成技术在电源模块中的应用

佐治亚理工大学 陈涵秋博士

13:55 - 14:20 Chiplever: Towards Effortless Extension of Chiplet-based System for FHE

中国科学院计算技术研究所 杜一博博士

14:20 - 14:45 基于CXL的高可扩展近存计算系统

华中科技大学 刘海峰博士

14:45 - 15:10 图像相似感知的三维混合键合AI加速器

清华大学 岳志恒博士

15:10 - 15:35 AIG-CIM: A Scalable Chiplet Module with Tri-Gear Heterogeneous Compute-in-Memory for Diffusion Acceleration

北京大学 贾天宇助理教授

15:35 - 15:50 茶歇

15:35 - 15:50 BeeZip: Towards An Organized and Scalable Architecture for Data Compression

中国科学院计算技术研究所 李雪琦副研究员

16:20 - 16:50 Accelerating Multi-Scalar Multiplication for Efficient Zero Knowledge Proofs with Multi-GPU Systems

山东大学 纪卓然助理研究员

论坛六 国产存算融合大芯片的发展路径

13:30 - 14:00 从自动驾驶到机器人的智能范式

北京辉羲智能信息技术有限公司 CEO 徐宁仪

14:00 - 14:30 混合键合存储芯粒:高效近存计算解决方案

兆易创新科技集团股份有限公司 CEO 胡洪

14:30 - 15:00 存算一体大算力芯片面临的技术挑战和解决策略

苏州亿铸智能科技有限公司 亿铸科技创始人、董事长兼CEO 熊大鹏

15:00 - 15:30 自旋轨道矩磁存储器和其在存算一体领域的应用

北京航空航天大学 张和副教授

15:30 - 15:50 茶歇

15:50 - 16:20 面向大芯片高密度集成的基板技术研究进展

中国电子科技集团第五十八研究所 高密度基板工程部经理 李轶楠

16:20 - 16:50 面向AI大模型的大算力存算融合芯片架构

清华大学 王扬助理研究员

16:50 - 17:20 面向图计算的存算融合并行计算架构与系统设计探索

华中科技大学 黄禹研究员

论坛七 芯片互连-突破P级算力瓶颈

13:30 - 14:00 一种片上网络的开源实现

北京开源芯片研究院 总工程师 王齐

14:00 - 14:30 混合增强计算的实践与思考

西安交通大学 任鹏举教授

14:30 - 15:00 基于三维堆叠的多芯粒高效能芯片设计

中国船舶集团公司第709研究所 熊庭刚 研究员

15:00 - 15:30 飞腾处理器存储及互连系统前后端融合的自动化设计方法探索

国防科技大学 曾坤 副研究员

15:30 - 15:45 茶歇

15:45 - 16:15 P级算力芯粒互联网络关键技术

中科芯集成电路有限公司 首席专家 魏敬和研究员

16:15 - 16:45 面向AI芯片的互连架构设计

上海交通大学 叶瑶瑶副教授

16:45 - 17:15 智算Scale-Up网络面临的挑战和关键技术

上海合见工业软件集团 副总裁 杨凯

17:15 - 17:45 圆桌讨论环节

论坛八 集成芯片互连微缩的路径及挑战

13:30 - 14:00 限域空间下的主动式半导体温控技术与芯片

中国科学院金属研究所 孙东明研究员

14:00 - 14:30 同步辐射X射线技术在半导体材料表征与器件缺陷检测中的应用

南开大学 罗锋教授

14:30 - 15:00 芯片-封装相互作用和可靠性

东南大学 李晗教授

15:00 - 15:30 晶圆级封装工艺技术在芯粒集成上的应用与发展

中国电科第五十八研究所 汤文学高级工程师

15:30 - 16:00 茶歇

16:00 - 16:30 常温键合技术在半导体器件制造中的应用

国家第三代半导体技术创新中心(苏州)首席科学院 梁剑波

16:30 - 17:00 芯粒-晶圆混合键合关键技术与装备研究

华中科技大学 吴豪副教授

17:00 - 17:30 基于电沉积铜互连微结构调控的互连技术研究

上海交通大学 吴蕴雯副教授

论坛九 三维集成热管理与可靠性

13:30 - 14:10 功率器件多物理场实时测量及“热-力-电-材”多学科整体优化设计

清华大学 张兴教授

14:10 - 14:50 芯片级热管理研究与展望

上海交通大学 吴慧英

14:50 - 15:30 Non-reciprocal heat transfer/thermal diode & its applications in solid state cooling

Shenzhen International Quantum Academy Baowen Li

15:30 - 15:50 茶歇

15:50 - 16:30 先进封装芯片级热界面材料的研究与应用

中国科学院深圳先进技术研究院 孙蓉研究员

16:30 - 17:10 集成电路封装中的热、应力传感器

中国科学院微电子研究所 焦斌斌研究员

17:10 - 17:50 基于失效物理的TSV/TGV互连可靠性研究

工业和信息化部电子第五研究所 周斌研究员

论坛十 顶会论坛-设计与工艺

13:30 - 13:50 A 64-Gb/s/pin PAM4 Single-Ended Transmitter with a Merged Pre-Emphasis Capacitive-Peaking Crosstalk-Cancellation Scheme for Memory Interfaces in 28nm CMOS

南方科技大学 潘权教授

13:50 - 14:10 A Monolithic 5.7A/mm2 91% Peak Efficiency Scalable Multi-Stage Modular Switched Capacitor Voltage Regulator with Self-Timed Deadtime and Safe Startup for 3D-ICs

清华大学 刘效森副教授

14:10 - 14:30 A 64-Gb/s Reference-Less PAM4 CDR with Asymmetrical Linear Phase Detector Soring 231.5-fsrms Clock Jitter and 0.21-pJ/bit Energy Efficiency in 40-nm CMOS

中国科学院半导体研究所 张钊研究员

14:30 - 14:50 A 0.43pJ/b 200Gb/s 5-Tap Delay-Line-Based Receiver FFE with Low-Frequency Equalization in 28nm CMOS

中国科学院深圳先进技术研究院 孙蓉研究员

14:50 - 15:10 COMB-MCM: Computing-on-Memory-Boundary NN Processor with Bipolar Bitwise Sparsity Optimization for Scalable Multi-Chiplet-Module Edge Machine Learning

复旦大学 朱浩哲助理研究员

15:10 - 15:40 茶歇

15:40 - 16:00 Signal Integrity Design Methodology for Package in Co-packaged Optics Based on Figure of Merit as Channel Operating Margin

宁波德图科技有限公司 教授级高工 蒲波

16:00 - 16:20 Heterogeneous Integration of Diamond-on-Chip-on-Interposer for High-Performance Thermal Management in Supercomputing 2.5D Chiplets Packaging

厦门大学助理教授 钟毅

16:20 - 16:40 Low melting point micro-nanoparticles for high-density microbump bonding technology

香港城市大学 毛星超博士

16:40 - 17:00 Cross-Scale reliability simulation of chiplet devices based on submodeling approach

哈尔滨工业大学 王韬涵博士

17:00 - 17:20 Ultra-high Frequency Acoustic Micro-imaging Simulation on Defect Detection at the TSV-Cu Bulk/Bonding Interface

武汉大学 王诗兆助理研究员

本次大会的媒体合作伙伴是半导体行业观察,芯思想,半导体产业纵横,未来半导体和创芯网(EETOP)。