近日,第70届国际电子器件大会(International Electron Devices Meeting,IEDM)在美国旧金山举行,本届会议的主题是“塑造未来的半导体技术”(Shaping Tomorrow's Semiconductor Technology),旨在展示微电子器件领域的最新原创工作。集成电路学院王欣然教授领导的南京大学-苏州实验室-华为海思联合团队在会议上发布了“将二硫化钼晶体管微缩至1纳米节点”(Scaling MoS₂ transistors to 1 nm node)的最新研究成果。

二维半导体是全球学术界和产业界公认最具希望的后摩尔集成电路非硅新材料之一,被国际器件与系统路线图(IRDS)明确为1nm及以下节点的沟道材料。当前,该领域正处于从基础研究向产业应用过渡的关键阶段,为我国集成电路赛道转换和技术超越提供了机遇。集成电路制程“节点”是由晶体管接触栅间距(CGP,包括沟道长度+接触长度+2×栅源间隔长度)定义的,根据IRDS,1nm节点晶体管CGP必须缩小至40nm,超越了硅基CMOS器件尺寸微缩极限。

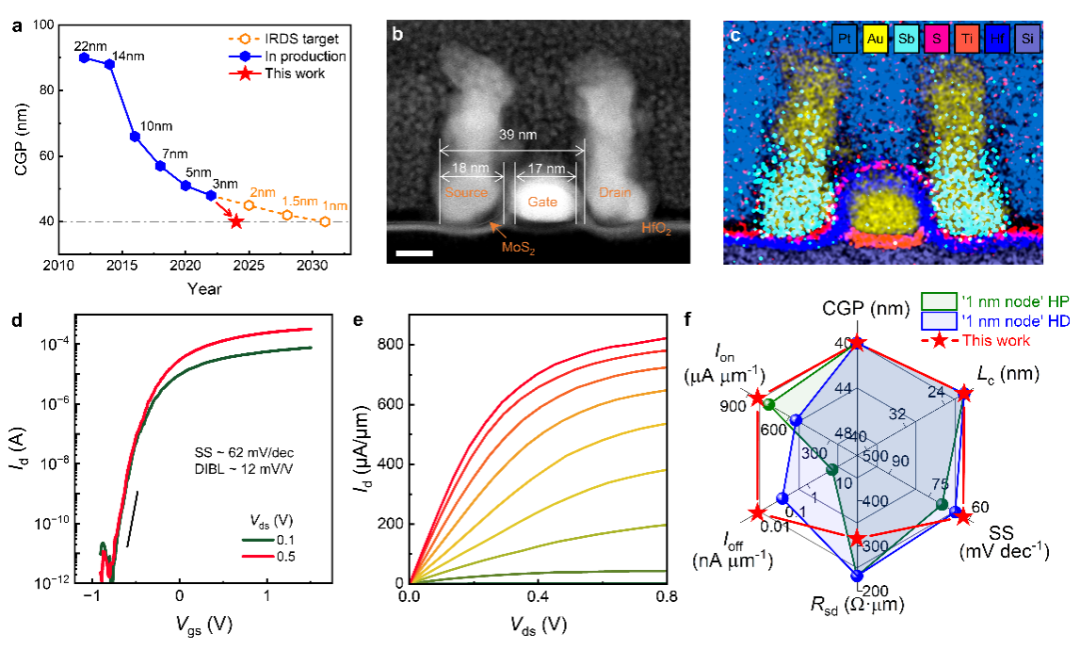

图1 1nm节点MoS₂晶体管。a. 集成电路晶体管CGP的演变趋势。b-c. 1nm节点MoS₂晶体管的剖面STEM和EDS表征。d-e. 1nm节点MoS₂晶体管的转移曲线和输出曲线,展现优异的电学特性。f.与IRDS 1nm节点晶体管的性能-尺寸对比。

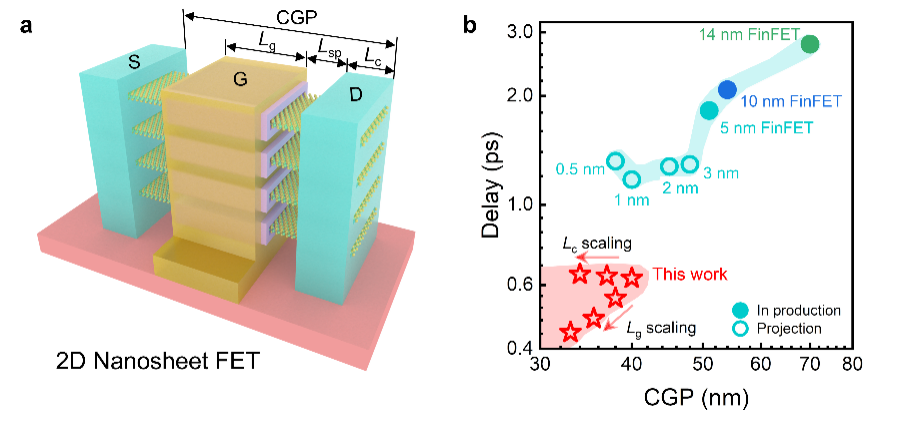

为突破1nm节点晶体管器件,团队在前期二维半导体材料和接触技术重大原理突破的基础上(Nature Nanotech. 16, 1201 (2021), Nature 613, 274 (2023)),从产业需求出发,开发出高纯度半金属欧姆接触外延沉积工艺,突破了极限尺寸下接触电阻记录,在20nm接触长度下实现接触电阻小于100Ω·μm。结合亚20nm超短沟道,在国际上首次成功研制出CGP为40nm的高性能MoS₂场效应晶体管,在0.6 V源漏偏压下具有0.79 mA/μm的高驱动电流,大于10⁷的开关比,小于10 pA/μm的关态电流,62 mV/dec的亚阈值斜率和12mV/V的漏致势垒降低效应。该器件在性能-功耗-尺寸(PPA)关键指标上满足了1nm节点技术要求,充分展示出二维半导体在先进制程集成电路中的技术潜力。进一步的TCAD模型仿真预测,四层堆叠MoS₂ 纳米片晶体管与1nm节点的 Si CMOS 相比,可将栅极延迟减少 46.6%,展示出二维半导体在路线图终点的卓越缩放潜力。该成果与英特尔、台积电、三星等产业巨头的最新成果同台发布,是本届大会二维半导体器件分会中国大陆唯一入选的研究成果(IEEE IEDM, 24.7, 1-4)。

图2 基于多层堆叠环栅晶体管(GAAFET)的TCAD仿真和性能预测

国际电子器件大会

国际电子器件大会(International Electron Devices Meeting, IEDM)始于1955年,是微电子器件领域的顶级会议,在国际半导体技术界享有崇高的学术地位和广泛的影响力,被誉为“微电子器件领域的奥林匹克盛会”。该会议主要报道国际半导体技术和微电子器件方面的最新研究进展,是高校、研发机构和行业领军企业发布其技术突破的重要平台。该会议每年举办一次,是全球半导体行业关注的焦点。

LIMIT团队

低维信息材料与集成电路(Low-dimensional Information Materials and Integrated circuit Technology, LIMIT)团队由国家杰青、长江学者、IEEE Fellow王欣然教授领衔,包括国家青年人才7人。团队持续推进有组织科研,过去10余年围绕二维半导体“材料制备-器件工艺-集成技术”全链条开展关键技术研究,取得了系统性成果:突破二维半导体大面积单晶制备技术;创新发展了界面修复、欧姆接触、介质层集成等一系列关键器件工艺,研制出1nm节点晶体管器件;研制出二维半导体集成电路与类脑计算芯片,开拓了新材料在下一代信息技术中的应用。团队近5年发表Nature正刊2篇,Nature子刊20余篇,授权中美专利10余项。3项成果被写入国际半导体技术路线图,10次入选高被引学者榜单。

评论

文明上网理性发言,请遵守新闻评论服务协议

登录参与评论

0/1000