ICCAD-Expo

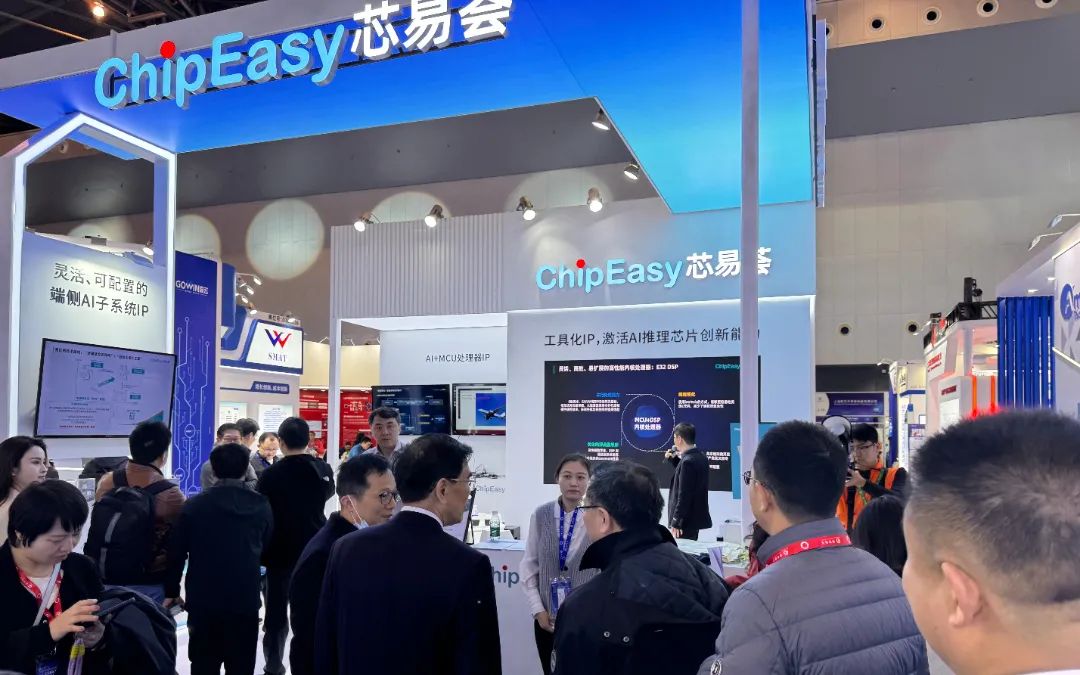

12月11日至12日,中国集成电路产业年度盛会“ICCAD-Expo 2024”在上海世博展览馆盛大举行。本次大会以“智慧上海,芯动世界”为主题,汇聚了6000余位全球业界人士。芯易荟作为国产EDA+IP领域的实力派,在本次展会中展示了多项创新成果,并通过重量级演讲与上下游合作伙伴共话新形势下集成电路产业发展。

01 EDA与IC设计服务论坛EDA and IC Design Forum

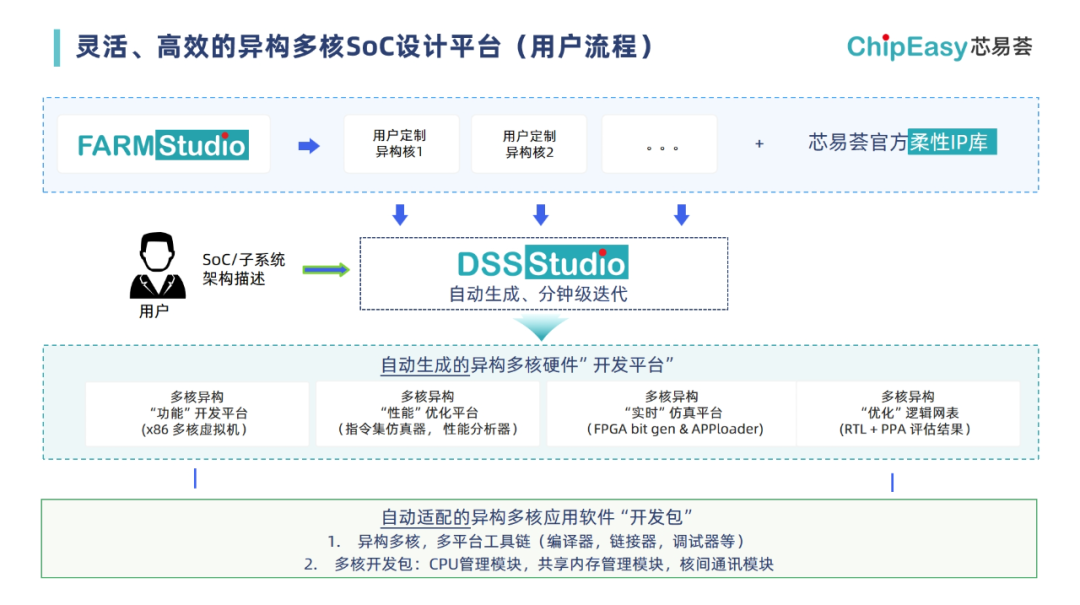

芯易荟研发副总裁张卫航发表了主题为 “异构多核设计平台,激活大规模AI系统架构创新能力” 的重要演讲,分享了芯易荟在异构多核 SoC 设计平台上针对 AI 系统架构创新的最新进展与成果,为 AI 芯片技术发展提供了新的思路与解决方案。演讲中,张卫航首先回顾了 SoC 设计的发展历程,深入分析了当前 AI 芯片面临的痛点与挑战。他指出,在快速发展的AI浪潮下,架构更新缓慢、验证过程耗时漫长以及存储瓶颈等问题已成为制约AI芯片进一步发展的重要因素。

针对这些挑战,芯易荟推出了 FARMStudio 和 DSSStudio 两款核心工具,分别专注于定制处理器与子系统设计。这两款平台提供了从协同设计到多层级定制的全方位解决方案,其多核异构工具套装集成了多种先进的开发平台与工具包,极大地提升了端侧AI芯片设计的灵活性与效率。此外,张卫航还详细介绍了芯易荟官方柔性IP 库中的多系列 IP 产品,展示了其在性能、可配置性等方面的显著优势与创新亮点。他表示,这些 IP 产品不仅为端侧AI芯片设计提供了丰富的功能模块选择,还可以通过芯易荟提供的配套工具拓展指令,实现定制化功能,满足了 AI 时代多元化、复杂化的应用需求。

02 IC设计与创新应用论坛IC Design & Innovation Application Forum

芯易荟副总裁石贤帅博士以主题《灵活、可配置的端侧 AI 推理处理器子系统 IP》发表精彩演讲。石贤帅博士深入介绍了芯易荟自主开发的灵活可配置的端侧 AI 推理处理器子系统 IP。当前,AI 模型正呈现出快速迭代的趋势,其发展速度远超传统芯片架构的更新步伐,给芯片设计领域带来了巨大挑战。对此,芯易荟凭借深厚的技术积累与创新思维,提出了一系列极具前瞻性的解决方案。其中,硬件子系统及软件工具链的自动生成显著提升了芯片对不同 AI 模型的适配能力,无需繁琐的手动调整,即可快速响应模型变化;多层次自动化验证则有效保障了芯片设计的准确性与稳定性,大幅缩短了验证周期,减少了潜在的设计风险;而适配存储需求的架构优化更是直击芯片存储瓶颈的关键痛点,使芯片在数据存储与读取方面更加高效流畅。

这些创新性技术的综合应用,不仅成功缩短了AI 芯片的设计周期,减少了研发过程中的时间与资金投入,还极大地提升了整个系统的适配性与可靠性。在演讲中,石贤帅博士展示了一个引起全场高度关注的数据——芯易荟AI子系统IP在LLAMA2 7B推理的模型下,单位算力推理性能可达45 Token/s/TOPs,并且算力规格灵活可定制。他强调,芯易荟正在积极布局专注端侧AI推理芯片的工具化IP,助力AI产业加速迈向新的发展高度。

03 展会焦点Exhibition

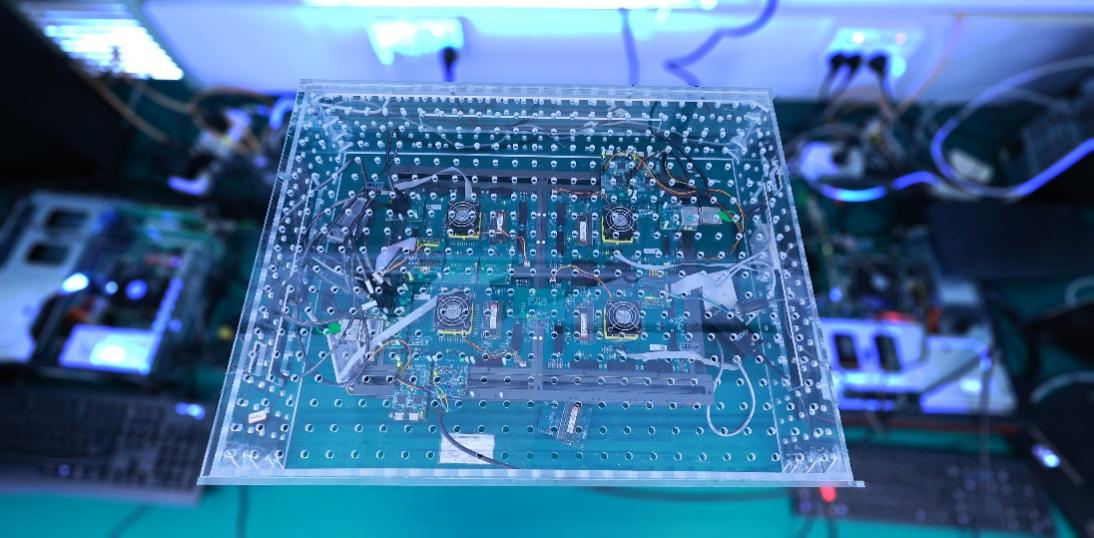

展会期间,芯易荟展位成为焦点之一,集中展示了依托FARM(Flexible Advanced RISC Machine)技术自主研发的系列异构多核设计工具,包括全球首款C语言描述基于RISC-V基础指令集的DSA处理器生成工具FARMStudio、以及多核异构子系统设计工具DSSStudio。此外,还展示了芯易荟面向AI、音频、工业控制、大模型推理等领域的E32系列AI+MCU IP、AI子系统IP等产品。

多核异构是当下芯片设计的主流趋势,也是芯易荟技术研发的重点所在。芯易荟充分发挥自身在处理器设计方面的核心优势,聚焦高性能运算模块设计、异构多核子系统设计、柔性IP库组成的基础技术平台的搭建和打磨,赋能产业合作伙伴,加速“重芯定易”时代的到来。