近日,以北京大学集成电路学院为第一完成单位的16篇论文在美国新泽西举行的第43届国际计算机辅助设计会议(ICCAD 2024)上发表,北京大学集成电路学院也成为国际上在ICCAD 2024以第一单位录取论文最多的单位。

这16篇论文内容涉及新型EDA算法、人工智能调度、映射和加速器设计方法、人工智能隐私计算等多个学术前沿领域。同时,梁云、林亦波、李萌等多位学院老师为会议TPC成员,李萌、林亦波老师为会议分论坛主席。

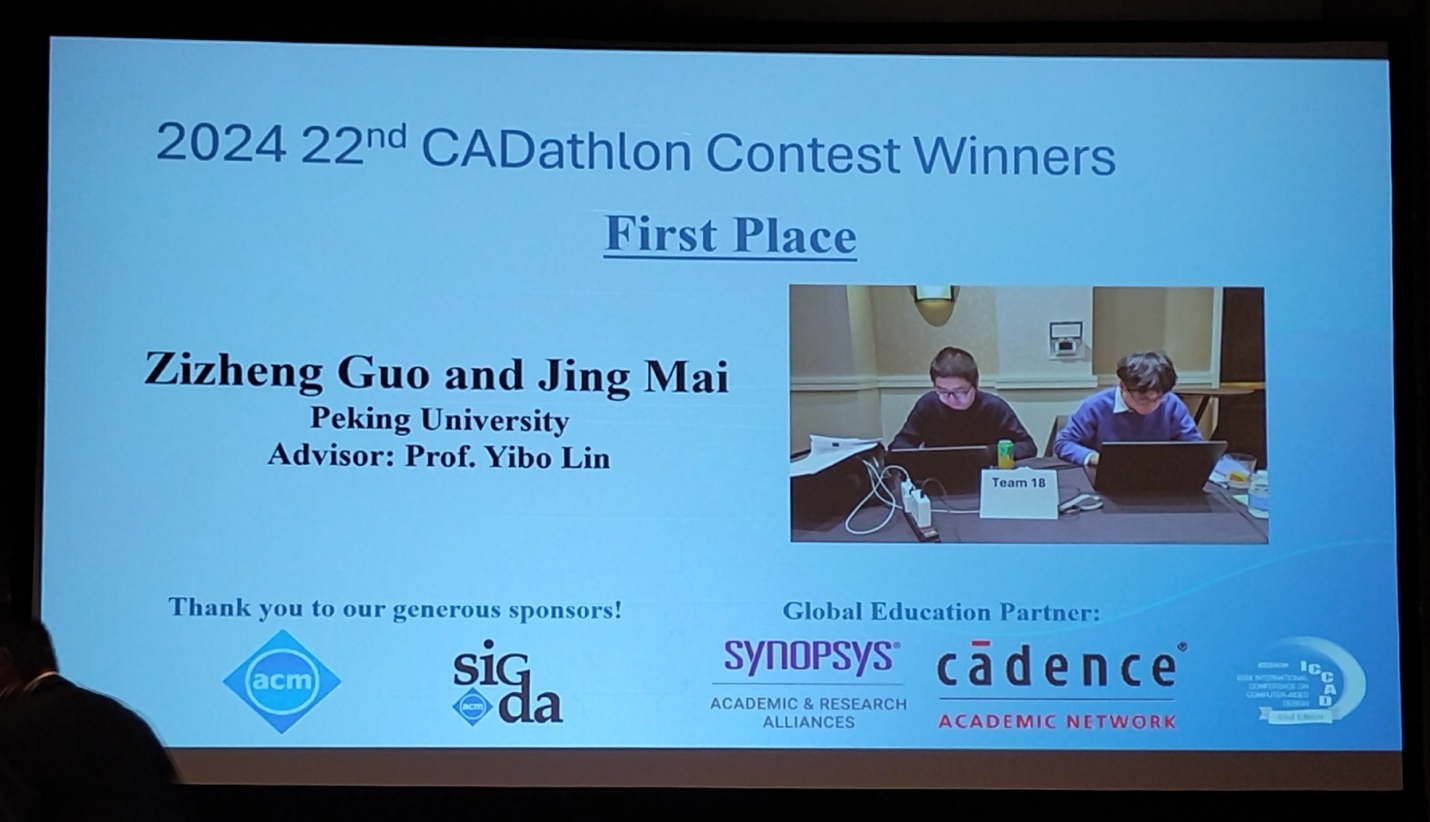

林亦波老师指导的博士生麦景、郭资政参加ICCADCADathlon编程竞赛获得第一名,本科生杜宇凡和博士生郭资政参加ICCADCADContest获得赛题三“ML/GPU加速逻辑门尺寸优化”赛道第一名。此外,杜宇凡和郭资政的论文《Fusion of GlobalPlacement and Gate Sizing with Differentiable Optimization》获得最佳论文提名。

部分参会师生合影

博士生郭资政、麦景获得ICCADCADathlon编程竞赛第一名

本科生杜宇凡、博士生郭资政获得ICCADCADContest赛题三“ML/GPU加速逻辑门尺寸优化”赛道第一名

新型EDA算法方向发表论文(共8篇)总结如下:

01.融合逻辑门布局和尺寸调整的可微优化技术

随着半导体技术微缩,优化电路的性能、功耗和面积指标(PPA)愈发具有挑战性。三者间的平衡问题也不容忽视。传统的设计流程将布局与逻辑门尺寸调整分为独立的阶段。这种分立的流程通常会导致设计优化空间的局限性。针对这一问题,林亦波研究员-王润声教授研究团队提出了一种新型融合优化技术,将布局与逻辑门尺寸调整统一到一个可微优化框架中,并实现了GPU异构加速的PPA目标优化。实验结果表明,该模型在时序指标TNS和WNS上分别实现了77.1%和43.5%的提升,同时静态功耗降低了1%。此外,该方法较传统基于CPU的设计流程提速最高达7倍,可以更高效地支持复杂电路设计与优化的需求。该工作以《Fusion of GlobalPlacement and Gate Sizing with Differentiable Optimization》为题发表,获得了本届ICCAD最佳论文提名(本科生杜宇凡和博士生郭资政为共同第一作者,林亦波研究员为通讯作者)。

02.HeteroExcept: 支持时序例外分析的CPU-GPU异构静态时序分析算法

大规模集成电路的静态时序分析需要大量处理虚假路径(FalsePath)、多周期路径(Multi-CyclePath)和其他类型的时序例外规则,使得静态时序分析效率大幅降低。尽管时序传播是线性时间复杂度的算法,然而一般时序例外规则导致静态时序分析成为NP难问题,只能通过标签图传播的启发式算法进行计算。传统基于CPU的标签图传播算法由于并行度限制,效率低下。为了克服运行时间的挑战,林亦波研究员-王润声教授研究团队提出了一种通用的CPU-GPU异构时序分析算法HeteroExcept,可以处理常见类型的路径例外规则,高效生成准确的路径报告。该算法能够处理高达数千条时序例外规则和数百万规模元件的电路。HeteroExcept在CPU和GPU之间引入了高效的投机数据交换策略,提出了包括时序例外影响范围确认、标签结构写时复制等技术,在标签图传播过程中实现了有效的剪枝。与工业级时序分析工具PrimeTime和OpenSTA相比,HeteroExcept将效率分别提高了6.8倍和12.9倍。该工作以《HeteroExcept: A CPU-GPU Heterogeneous Algorithm to Accelerate Exception-aware Static Timing Analysis》为题发表(博士生郭资政为第一作者,林亦波研究员为通讯作者)。

03.FaStTherm: 考虑非线性效应的稳定芯片瞬态热预测技术

随着芯片集成密度的不断提高,热问题变得愈发严峻,包括非线性静态功耗以及非线性热导率在内的片上非线性热效应也变得愈发显著。高效准确的瞬态热仿真是解决芯片热问题的基础之一。由于传统的数值方法时间资源开销过大,研究人员提出了多种基于深度学习的快速瞬态热预测模型。然而,这些模型普遍面临着误差累积的问题,在时间步长较多时,缺乏稳定性,难以应对真实场景下的工作负载,尤其是在考虑片上非线性热效应的情况下。针对这一问题,林亦波研究员-王润声教授研究团队提出了FaStTherm,一种稳定的快速芯片瞬态热预测模型。FaStTherm采用自编码器架构在隐空间进行模型降阶,从而实现了快速瞬态热预测。在此基础上,FaStTherm提出了一种基于谱归一化的全局稳定策略,和基于多步展开训练以及噪声注入的局部稳定策略,显著减少了误差累积效应,提高了长期稳定性。和商业仿真工具COMSOL相比,FaStTherm实现了10000倍的预测效率提升。与此同时,相比于现有瞬态热预测模型,有效预测步数增加了42到73倍。该工作以《FaStTherm: Fast and Stable Full-Chip Transient Thermal Predictor Considering Nonlinear Effects》为题发表(博士生朱天翔为第一作者,林亦波研究员为通讯作者)。

04.HeLEM-GR: GPU异构加速全局布线技术

全局布线是芯片物理设计中关键的一步,在物理设计各个阶段应用广泛。随着芯片规模不断增大,设计结构越来越复杂,导致目前基于CPU的全局布线算法求解效果差,运行时间长,严重影响了物理设计的质量和效率。林亦波研究团队提出了GPU异构加速全局布线工具HeLEM-GR。通过设计适用于GPU异构计算加速的求解框架和布线核心新算法,显著地提高了求解质量和运行效率。相比于国际物理设计竞赛ISPD 2024 Contest前三名队伍,HeLEM-GR在求解质量上提高了4.8%-5.8%,运行效率上提高了1.62-2.07倍。在超过5千万个线网的布线案例上,性能和效率表现尤其突出。研究成果以《HeLEM-GR: Heterogeneous Global Routing with LinearizedExponential Multiplier Method》为题发表(博士生赵春源为第一作者,林亦波研究员为通讯作者)。

05.MORPH:考虑混合区域约束的鲁棒芯片布局算法

现代芯片布局工具通常涉及三种类型的区域约束:默认区域约束、栅栏区域约束和引导区域约束。这些区域约束对布局算法构成了重大挑战,并成为近年来备受关注的问题。目前, 大多研究仅关注单一的栅栏区域约束,未关注实际设计中更常见的混合区域约束。区域约束容易导致现有算法陷入局部最优而难以进一步优化。在此背景下,林亦波研究员-王润声教授研究团队开发了一种基于二阶梯度信息的混合区域约束鲁棒布局算法——MORPH。该算法首次将混合区域约束整合到一个统一的多静电系统模型中,并提出了一个包含二阶信息的鲁棒非线性全局布局框架,以解决收敛性问题。在ISPD 2015测试数据集上的实验表明,MORPH实现了5.6%至14.3%的线长提升,降低了10%至24%的布线拥塞,并表现出更为稳定的收敛性。该研究以《MORPH: More Robust ASIC Placement for Hybrid Region Constraint Management》为题发表(博士生麦景为第一作者,林亦波研究员为通讯作者)。

06.ATPlace2.5D:面向2.5D芯粒系统的热感知布局技术

2.5D-IC通过集成多个Chiplet芯粒以降低计算系统的成本,并提高整体性能。但是高度集成的芯粒系统往往难以权衡性能和温度,限制了进一步的大规模集成。林亦波研究员-王润声教授研究团队提出了一种面向大规模2.5D-IC的热感知芯粒布局框架ATPlace2.5D。该算法提出一种基于物理模型的集约热模型,指导布局框架优化芯粒位置和旋转角度,提供平衡总线长和温度的布局方案。实验结果表明,ATPlace2.5D可以在几分钟内处理超过60个芯粒的2.5D-IC系统,并且最大温度和总线长分别较现有算法TAP-2.5D优化了5%和42%,效率提升了23倍。这一进展有望推动大规模2.5D-IC自动设计的发展。相关成果以《ATPlace2.5D: Analytical Thermal-Aware Chiplet Placement Framework for Large-Scale 2.5D-IC》为题发表(博士生王启盼为第一作者,林亦波为通讯作者)。

07.面向数模混合信号电路的多层次联合布局优化方法

数模混合信号电路用途广泛,包括新兴的自动驾驶和物联网等,这些应用场景要求数模混合信号电路的设计实现自动化和快速迭代。然而,数模混合电路设计通常需要大量人工介入进行定制设计,导致设计周期长。为提高设计效率,满足各类设计指标,林亦波研究员-王润声教授研究团队提出了一种多层次联合布局优化方法,可同时对各个电路层次进行布局,并考虑包括面积、线长、对称性、线性与信号流在内的多种布局约束。在多个不同类型的电路上,实验结果表明,该方法可以在几分钟时间内完成布局,实现与人工设计版图接近的电路后仿真性能。该工作以《Joint Placement Optimization for Hierarchical Analog/Mixed-Signal Circuits》为题发表(博士生高笑涵为第一作者,林亦波研究员为通讯作者)。

08.基于代码强化和自反思的大模型RTL代码生成

随着大规模语言模型(LLM)技术的快速发展,GPT-4和Claude3-Opus等商业模型在RTL(寄存器传输级)代码生成领域展现出了巨大潜力。然而,这些商业模型往往面临隐私和安全方面的问题。虽然开源LLM能够解决这些顾虑,但由于缺乏高质量的RTL训练数据集,其在代码生成任务上的表现远逊于商业模型。针对这一问题,梁云团队提出了一个全新的开源框架OriGen,通过代码增强和自反思机制显著提升了RTL代码生成的质量。OriGen通过基于知识蒸馏的代码到代码增强方法,有效扩充了开源RTL代码数据集的规模和质量。同时,该框架开发了基于编译器反馈的自反思机制,能够有效识别和修正代码中的语法错误。基准测试结果表明,OriGen大幅超越之前的最佳开源模型,达到先进商业模型的水平,并在自反思能力评估基准上超越了GPT-4达18.1%。该工作以《OriGen: Enhancing RTL Code Generation with Code-to-Code Augmentation and Self-Reflection》为题发表(博士生崔璠为第一作者,梁云教授为通讯作者)。

人工智能调度、映射和加速器设计方向发表论文(共6篇)总结如下:

01.HG-PIPE:使用混合粒度流水线的视觉转换器模型加速技术

视觉转换器是目前最为流行的用于计算机视觉任务的神经网络主干,在多种场景中有着广泛的应用。在一些端侧应用如自动驾驶和虚拟现实等应用中,推理延迟是极其重要的指标,典型延迟需求在10ms左右。然而视觉转换器模型的体量通常比卷积网络模型大出一个数量级,这对于硬件平台的性能和算法加速方案提出了严峻的考验。在专用的硬件架构设计中,流水线架构是一种常用的设计方案,在多阶段的神经网络推理中起到降低推理延迟的效果。然而视觉转换器的特性导致目前的流水线方案的硬件实现较为困难,可能导致极大的片上缓存代价与潜在的流水线气泡。为解决该问题,李萌研究员-王源教授研究团队提出一种混合粒度流水线技术,解决视觉转换器模型中由于注意力机制引入的全局依赖性导致的粒度冲突问题,在低硬件代价下实现了无气泡的流水线推理。通过在FPGA平台上的实现,该方案相较于v100 GPU快出2.81倍,比此前最先进的视觉转换器加速方案快出2.72倍。在先进FPGA平台上,该加速方案的延迟低至1.94ms,以支持各种延迟敏感应用。该工作以《HG-PIPE: Vision Transformer Acceleration with Hybrid-Grained Pipeline》为题发表(博士生郭晴宇为第一作者,李萌研究员和王源教授为通讯作者)。

02.OSCA:使用随机计算提升计算精度与硬件效率的神经加速器

近年来,人工智能技术的飞速发展对高效神经网络加速器的需求日益增长。作为一种极具潜力的新型计算架构,随机计算被不少研究者用来设计具有极高硬件效率的神经网络加速器。然而,传统的随机计算加速器面临严重的精度挑战,主要是由于比特流乘法和加法中的误差以及激活函数单元不兼容先进模型所需非线性非单调激活函数,这反过来又影响了加速器的硬件效率。李萌研究员-王润声教授研究团队提出了一种名为OSCA的新型端到端串行随机计算神经加速器。该加速器通过自适应量化累加,相关性无关乘法和创新的分段激活函数单元,显著提高了计算精度和硬件效率。在和串行加速器对比中,OSCA降低了30.18%均方根误差的同时还降低了87.75%的硬件代价;与更精确的并行加速器相比,OSCA降低了92.05%的硬件代价,面积效率提高了12.54倍的同时,推理精度提高了0.44%和0.86%。相关研究成果以《OSCA: End-to-end Serial Stochastic Computing Neural Acceleration with Fine-grained Scaling and Piecewise Activation》为题发表(博士生胡逸轩为第一作者,李萌研究员为通讯作者)。

03.大模型Chiplet的架构电源协同优化

大规模语言模型(LLM)对高效能和高性能硬件的需求,推动了可扩展Chiplet芯粒技术的发展,对功耗的优化和管理提出了更高的需求。黄如院士-叶乐教授、贾天宇研究员团队提出了一种针对LLM应用的芯粒设计层次化电源供电的协同优化和管理方法。为了模拟LLM的工作负载映射和电源供应,该方法首先建立了一个可扩展的芯粒系统模拟器,该模拟器展示了不同的电源策略对效率有显著影响,需进行电源管理、硬件架构、与映射策略的协同设计和优化。该方法进一步开发了一个面向芯粒系统的电源管理优化框架ScalePoM。根据给定的LLM模型以及性能、功耗、面积(PPA)需求,ScalePoM可以自动探索芯粒系统的架构和工作负载映射,以实现最优的层次化电源管理。该协同优化方法通过评估两种具有不同互连拓扑的可扩展LLM芯粒系统,实现了大型语言模型推理过程中平均45%和最高62%的能耗节省。该工作以《HierarchicalPowerCo-OptimizationandManagementforLLMChipletDesigns》为题发表(博士生董彦池为第一作者,贾天宇研究员为通讯作者)。

04.AdapMoE:基于敏感度分析和自适应专家选择与管理的混合专家模型高效推理技术

混合专家模型(MoE)通过稀疏激活减少了大语言模型的计算需求,但在边缘设备上部署时面临权重存储需求过高的问题。许多研究尝试通过将模型权重卸载到更低级存储,在需要时按需加载的方式进行部署。然而,现有的方法在处理混合专家模型这类具有高度动态性的任务时,具有极大的按需加载开销。李萌研究员-黄如院士团队提出了一个算法与系统协同设计的高效混合专家模型推理框架AdapMoE,旨在降低专家按需加载的延迟。AdapMoE创新性地采用了基于敏感度的自适应专家选择机制,动态调整激活专家的数量,并集成了高级预取和缓存管理技术,以减少加载延迟。AdapMoE在保持精度的前提下,将激活的专家数量减少了25%,并实现了1.35倍的端到端的加速效果。该工作以《AdapMoE: Adaptive Sensitivity-based Expert Gating and Management for Efficient MoE Inference》为题发表(博士生仲书璋为第一作者,李萌研究员为通讯作者)

05.ProPD:基于动态字符树剪枝与生成的大模型并行解码优化技术

生成式大语言模型由于自回归解码的特征,计算密度较低,从而面临着严重的存储带宽墙问题。为此,许多研究提出了并行解码方法,通过一次生成多个后续位置预测,继而并行验证的方式,缓解了存储带宽墙问题。但这类方法在保持上下文关系方面存在不足,尤其是在大批量处理下验证开销巨大。针对这一问题,李萌研究员-黄如院士团队提出了ProPD,一种基于动态字符树剪枝与生成的高效并行解码框架。ProPD通过引入早期剪枝机制,显著减少不必要的令牌验证开销,同时动态调整令牌树生成过程,以实时平衡计算量与并行度,优化不同批量和任务场景下的整体效率。在多个数据集和模型上的实验结果显示,ProPD在保证相同输出的情况下实现了1.1至3.2倍的加速效果。该工作以《ProPD: Dynamic Token Tree Pruning and Generation for LLM Parallel Decoding》为题发表(博士生仲书璋为第一作者,李萌研究员为通讯作者)

06.MCUBERT:考虑硬件资源的网络-调度-计算核协同优化技术

神经网络在边端微处理器上的部署与推理,具有低延迟、低能耗、隐私保护等特点,近年来成为备受关注的问题。由于微处理器在存储、内存资源上存在严格的限制,导致神经网络模型难以直接部署在微处理器上。近年来,不少研究尝试利用低比特量化、剪枝等手段降低推理开销。然而,现有的轻量化方法存在低准确率、需要专用计算核等问题。于此同时,传统的计算核设计与微处理器的适配性较低,造成较大的推理延迟。李萌研究员-黄如院士团队提出了一种网络-调度-计算核协同优化技术,首次将语言模型BERT部署在微处理器上,在MNLI测试数据集上实现了5.7倍的模型压缩和3.5倍的峰值内存占用压缩。同时通过计算核优化实现了1.5倍的模型推理加速。该工作以《MCUBERT: Memory-Efficient BERT Inference on Commodity Microcontrollers》为题发表(博士生杨泽斌为第一作者,李萌研究员为通讯作者)。

人工智能隐私计算方向发表论文(共2篇)总结如下:

01.FlexHE:基于同态加密的隐私推理核函数生成框架

基于同态加密的安全两方计算框架可以很好地保护数据隐私,并越来越多的被应用到了神经网络的隐私推理中。由于同态加密技术只能对多项式进行运算,现有研究通过手动设计的同态加密核函数来支持典型的神经网络算子。然而,考虑到不同的算子计算模式、输入输出尺寸,以及密码学参数,手动设计存在可扩展性差的问题,即对于某种特定场景与算子设计的核函数可能在其他场景下表现不佳甚至得到错误结果。李萌研究团队提出了一种自动化的同态核函数生成框架,实现了正确且高效的核函数生成。相比于此前的自动化生成框架以及手动优化的核函数,该工作最高实现了超过100倍以及8倍左右的延迟优化。该工作以《FlexHE: a Flexible Kernel Generation Framework forHomomorphic Encryption-Based Private Inference》为题发表(博士生俞江瑞为第一作者,李萌研究员为通讯作者)。

02.PrivQuant:基于协议与量化神经网络协同优化的通信高效隐私推理

基于安全二方计算 (2PC) 的私有深度神经网络 (DNN) 推理可为服务器和客户端提供安全的隐私保护。然而,现有的安全 2PC 框架由于大量通信而存在高推理延迟的问题。由于线性和非线性 DNN 层的通信随着权重和激活的位宽而减少,李萌研究员团队提出了 PrivQuant,通过联合优化基于 2PC 的量化推理协议和网络量化算法,可实现通信高效的私有推理。PrivQuant 针对通信密集型量化运算符的 2PC 协议提出了 DNN 架构感知优化,并进行图级运算符融合以减少通信。此外,PrivQuant 还开发了一种通信感知的混合精度量化算法,以提高推理效率同时保持高精度。网络/协议共同优化使 PrivQuant 的表现优于现有技术的 2PC 框架。通过大量实验,我们证明与 SiRNN、COINN 和 CoPriv 相比, PrivQuant 将通信量减少了 11 倍、2.5 倍和 2.8 倍,延迟减少了 8.7 倍、1.8 倍和 2.4 倍。(博士生许天识为第一作者,李萌研究员为通讯作者)。

背景介绍:

由电气电子工程师学会(IEEE)和美国计算机学会(ACM)共同举办的国际计算机辅助设计会议(ICCAD)被公认为EDA领域最重要的会议之一,享有很高的国际学术地位和广泛的影响力。该会议是探索EDA研究领域新挑战、展示前沿创新解决方案和识别新兴技术的重要论坛,涵盖了从器件和电路级到系统级的所有设计与自动化主题、以及后CMOS设计等新型方向。ICCAD 2024为第43届会议,于2024年10月27日至10月31日在美国新泽西举行。