9月23-24日,第二届设计自动化产业峰会IDAS在上海圆满举办。芯华章受邀参与数字芯片论坛,由产品与解决方案总监高世超就“项目与效率导向的多维验证解决方案”为主题分享在实际项目当中,与客户共同面对的挑战和实践案例。

大规模的系统级芯片设计由于场景丰富、系统规模不断扩张,需求正快速形成市场主流的大浪,涌向EDA工具并推动其不断革新。同时,从验证角度来看,产业面临着设计规模大导致的验证难以收敛,以及设计复杂度变大带来的调试困难。

当面对不同的芯片类型、设计的不同阶段,就需要不同层次的解决方案,并且通过不同的验证方法学,配合核心EDA工具链来支撑目前复杂的芯片验证任务。比如,从仿真时间上如何针对前仿,后仿性能痛点进行代码优化,从项目管理角度上、如何在EDA的帮助下缩小回归量,如何优化服务器资源管理来提高工程师下班时间的集群任务效率等。

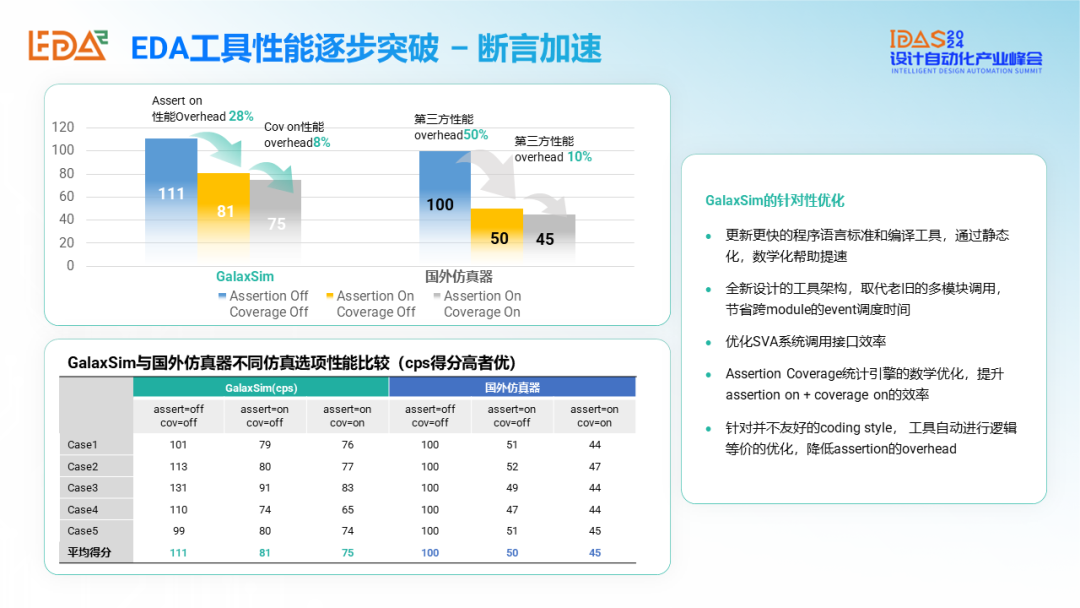

仿真器和调试器是验证工程师最常用且基石的两个工具,传统的软件仿真工具以调试功能强大著名,但却受限于仿真速度,不擅长处理系统级的大规模仿真验证。那么在仿真器行为精度达到项目需求的同时,如何提高性能,如加速仿真验证?从调试角度上,是否EDA可以提供更smart更自动化的问题定位分析技术以提高效率?

其中一个痛点就是断言加速,当设计公司为了提高内部信号检查的精确度,会选择加3%~5% RTL 代码量的断言(assertion)来辅助我们的行为检查,但是断言turn-on 以及它不同的代码风格会带来非常严重的runtime overhead。芯华章GalaxSim针对并不友好的coding style,能够自动进行逻辑等价的优化,以降低断言的overhead。

另外一个痛点则是如何在后仿阶段提升性能,当设计规模大到一定的程度,光网表的loading就是一件非常有挑战的步骤。由于要将所有时序、功耗、延迟与工艺和资产相关的物理参数等带入逻辑仿真中,后仿的速度通常是前仿的10倍左右降速,非常慢。芯华章后仿解决方案将从后仿编译、后仿单核仿真、后仿多核仿真以及后仿网表调试这些方面,着手提升后仿阶段的性能。

从模块级网表到SoC级网表,GalaxSim的门仿专用引擎及自研优化算法,助力提升网表仿真性能提升。

除此以外,值得一提的是GalaxSim对现有生态的支持。GalaxSim能提供更灵活的架构适配,与国产服务器紧密合作。

基于鲲鹏处理器等国产架构,芯华章逻辑仿真器GalaxSim、形式化验证工具GalaxFV,都能有效利用鲲鹏的高性能集群去提高编译与运算,在不同层次的性能和并行度,加速覆盖率收敛,显著提高系统级芯片仿真验证效率。

面对不断变化的市场需求和技术挑战,芯华章将持续致力于探索EDA工具的创新路径,为客户提供更加高效、可靠的验证解决方案。

通过与业界不同的芯片厂商的合作,芯华章希望能完成自身的演进,从“理解客户”到“引领客户”,也就是满足客户没有说出口的需求,成为客户最值得信赖的合作伙伴。