随着新一轮AI浪潮加速爆发,全球服务器市场持续繁荣,单台服务器的配置和性能也在逐步提升。中金报告指出,服务器出货量增加、AI服务器出货占比扩大,带动了内存接口芯片需求上涨,与此同时,DDR5渗透率提升以及子代迭代速度快对配套内存接口芯片及套片存在强需求。

作为CPU与硬盘之间的数据桥梁,内存模组在存储和读取速度方面的速度,在一定程度上决定了计算机整体性能的强弱。所以说,“要想富,先修路”这个道理在芯片领域依旧成立。

内存模组对于数据的处理能力影响了计算机的性能,而内存接口IP的设计和演变则决定了前者数据读取速度的快慢。

RAM存储器技术的跨越

从SRAM到DDR5 SDRAM的演变

半导体制造工艺的不断突破,从180纳米、90纳米到目前主流的28纳米再到更先进的工艺,为DDR SDRAM接口IP带来了更高的集成度和更优的性能。同时,市场竞争、消费者需求、国际标准化组织的规范更新,以及EDA工具的先进支持,都在促进DDR SDRAM接口IP的持续创新,以实现更高性能、更强可靠性和更高安全性,满足关键应用的高标准需求。

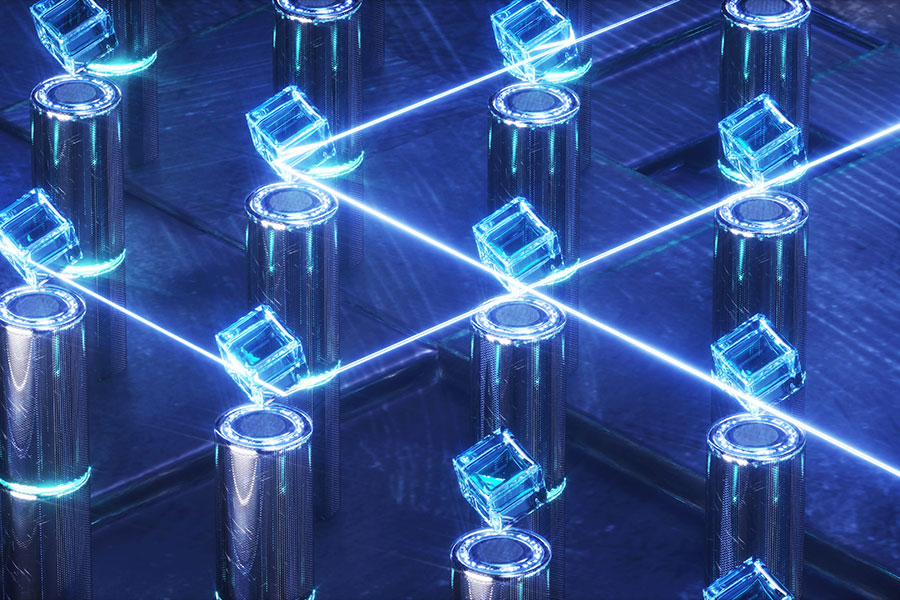

在存储器技术的发展历程中,SRAM(静态随机存取存储器)率先登场,其起源可追溯至20世纪60年代末的美国。多家企业投身于SRAM技术的创新与制造,其中Intel公司以其商业化步伐领先,于1969年推出了划时代的C3101型号SRAM产品——一款64位容量的存储器芯片,霍尼韦尔公司(Honeywell)是其主要客户。

DRAM(动态随机存取存储器)的发展则得益于以其独特的存储机制——单个晶体管搭配电容的设计,实现了成本的显著降低。相较于SRAM复杂的双稳态电路,DRAM在单位面积的存储密度上取得了飞跃,加之其存储单元无需持续供电,仅需周期性刷新即可维持数据,这使得DRAM在功耗上也展现出巨大优势。这些特性推动了DRAM的广泛应用和迅猛发展。

图1:DRAM与SRAM电路结构

数据显示,在180纳米至65纳米的四种技术节点中,DRAM单元的面积维持在19至26平方微米(F^2)的范围内。相较之下,典型的SRAM单元面积则在120至150平方微米(F^2),其中F代表工艺的特征尺寸。

2022年,英特尔(lintel)和AMD两大厂商的Alder Lake平台和Zen 4平台开始支持DDR5内存,代表了与最初的SRAM相比,技术有了巨大飞跃。

SRAM与DDR5

SDRAM器件结构革新和性能飞跃

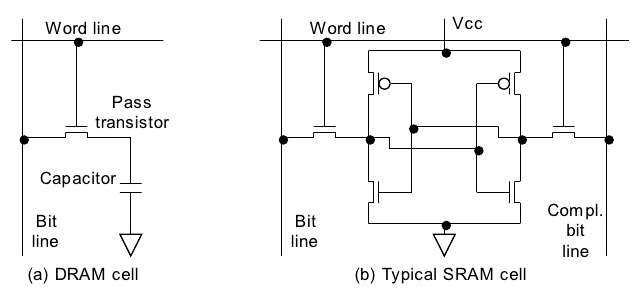

如下,通过一张直观的图表,可以深入了解从最初的SRAM到现代DDR5 SDRAM的演变历程。最初的SRAM颗粒,以其基础的"16X4"阵列结构,仅提供了64位的存储能力,这在当时的技术水平下,仅足够容纳8个英文字符或4个汉字。其工作频率仅达到大约10MHz,是早期存储技术的起点。然而,随着技术的飞速发展,现代DDR5存储器件的单芯片容量已经实现了惊人的64Gbit存储容量,而其输入/输出速率更是达到了8800Mbps的高峰,这一飞跃不仅展示了存储技术的巨大进步,也满足了当代高速数据处理的需求。

图2:SRAM与DDR5 SDRAM颗粒内部结构对比

以上仅仅描述了存储器芯片的一个颗粒(Chip)的结构。在颗粒基础上,形成内存条(比如SIMM(单列直插内存模块)、DIMM(双列直插内存模块)、RDIMM(Registered DIMM,寄存式双列直插内存模块)),内存条进一步组合成更为复杂的模组(Memory kit),或许再搭配多通道用于PC或者服务器的母版(Matherboard),最终组成现代计算机复杂的内存系统。

图片以Kingston公司近期发布的KF556R36RBK8-256为例,这是一个8通道的R-DIMM内存模组,每通道容量为32GB,总计达到惊人的256GB。256GB的容量意味着,如果全部用于缓存汉语文本数据,那么它能够存储约1350亿个汉字,相当于中文最长小说字数(500万字)的数万倍。AI训练时,每生成一个token需要把模型在内存中读出一遍,若256GB的内存仅仅用于缓存AI大模型参数,假设每个参数占用1Byte,那么它能够支持高达2700亿个参数的AI模型训练,其数量超过了当前最大的AI模型——仅130亿参数。服务器领域的LRDIMM内存,结合多Die堆叠设计,拥有40个颗粒的LRDIMM内存最大容量将达到8GB x 8次 x 40个颗粒=2560GB=2TB,再进一步,成千上万的服务器组成的庞大算力集群,无疑将对海量数据缓存应用提出巨大需求。此时,内存接口芯片在这些应用中发挥的关键作用变得尤为重要。

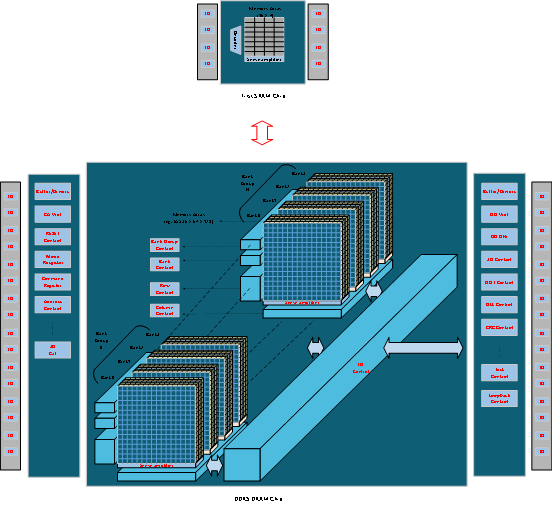

图3:典型服务器的数据缓存子系统

DDR SDRAM接口IP

技术迭代

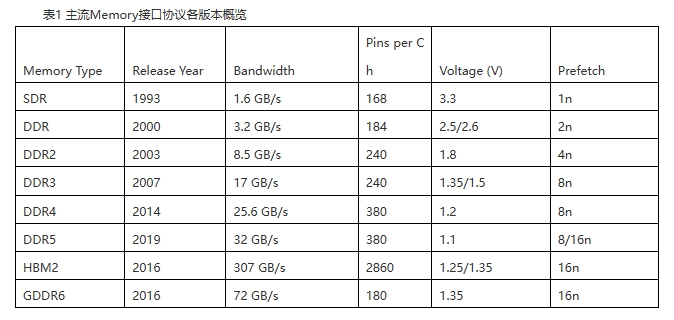

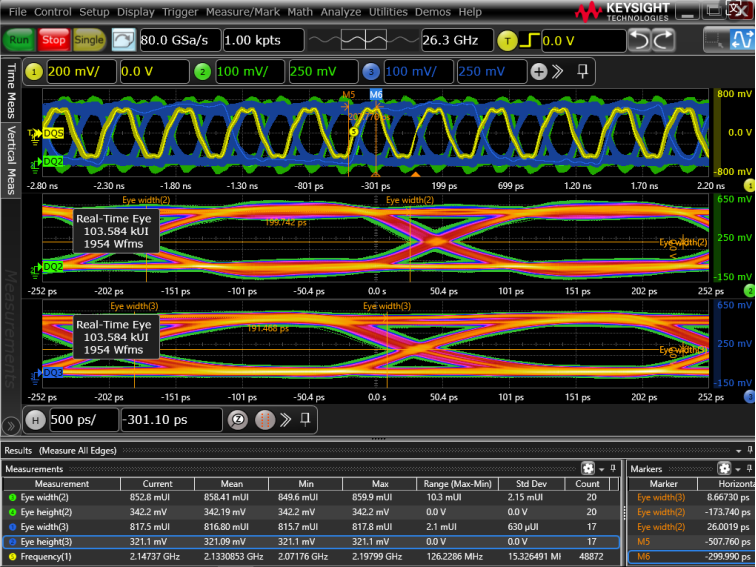

SDRAM(同步动态随机存取存储器),作为DRAM内存技术的一个分支,自20世纪70年代起便开启了其演进之旅。从最初的SDR SDRAM起步,技术不断革新,直至今日的DDR5 SDRAM,以及即将问世的DDR6 SDRAM,还衍生出了多样化的分支,以满足不同应用场景的需求。例如,LPDDR系列专为移动设备设计,以低功耗为特点;GDDR系列则针对显卡和GPU,提供卓越的图形处理性能;HBM和UCIe技术则为数据中心、自动驾驶、人工智能推理和训练等高端应用提供了高容量、高带宽和低延迟的解决方案。

若从速率的角度,我们可以概括出每一代内存芯片的速率参数如下。(其中,"module name"是厂商代表内存模块的名称或标识,同时指示内存条的规格和性能特征)

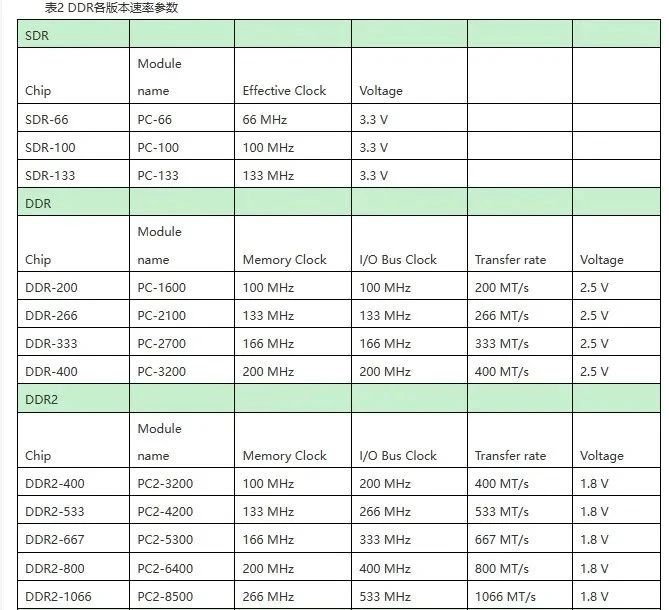

同步于DDR器件的发展,DDR高速接口IP作为DDR器件的控制部分,DDR高速接口IP的演进过程中其Feature支持DDR的是四个“更”:更大的容量、更快的速率、更可靠的数据和更高的能效。

图4:DDR4到DDR5的演进

通过改良工艺,优化存储单元阵列的组织结构和组织方式,每一代的容量都有至少翻倍的增加。每一代DDR IO接口速率以及数据的Burst Length(突发传输长度)都有翻倍的增加,精细的颗粒度划分、Bank Group、Bank和阵列的结构优化,使得DRAM器件需要的precharge(预充电)和refresh(刷新)操作的时序开销得到有效的控制,从而提升有效传输的速率。

在演进过程中,越来越精准的时序单元方案、高精度的校准Training算法设计、精细有效的单元电路参考电压设计、各种数据错误检测以及数据校正方案被引入。比如PAR(parity check)、CRC(循环冗余校验,Cyclic Redundancy Check)校验可以及时报告异常,再如ECC(错误校正码,Error-Correcting Code)可以在一定程度下修复错误的数据比特位,高速场景中引入DFE(Decision Feedback Equalization)等,使得数据在高速传输过程中对抗串扰、电磁干扰,保证信号完整性。

随着DDR技术的迭代,从最初的DDR到现在的DDR5,每一代的操作变得更加灵活高效。DDR5在Refresh操作上引入了Same Bank Refresh,采用了更高效、更智能的刷新算法,包括温度传感器监测补偿和独立的电源管理,减少了刷新等待的延迟,提高了通道利用率,降低了性能开销。同时,更低的工作电压进一步提升了能效比。这一演进过程不仅展示了DDR内存芯片在技术挑战中的持续成长,也彰显了DDR接口芯片作为桥接部分在技术创新中的重要作用。

牛芯半导体

DDR技术的创新和突破

牛芯半导体在DDR技术不断演进的历程中,紧跟行业发展趋势,致力于自主研发DDR PHY&MAC的全面解决方案。牛芯半导体在每一代DDR协议的演进中都展现出了积极的投入和显著的突破,实现了对现有DDR协议的全面兼容,包括DDR2/3/4/5和LPDDR2/3/4/4X/5等。

牛芯半导体的自研产品不仅可以确保对DDR接口协议的兼容性,同时也兼顾了信号完整性(SI)和电源完整性(PI)、训练算法以及高速DDR I/O的精密设计。在DDR4、LPDDR4或更高速度协议的实现中,引入了2D VREF Training技术,以寻找到数字眼图裕量最大的设定,进一步提升系统性能。同时,针对温度和电压的变化,可以自适应进行Delay line的实时补偿,确保系统的稳定与高效。

得益于在SerDes高速接口领域的深厚积累,牛芯半导体正将SerDes接口中使用的Tx FFE(前向反馈均衡)和Rx DFE(判决反馈均衡)模块逐步应用到DDR技术中,不断推动创新的边界。

牛芯半导体的DDR MC+DDR PHY combo IP在国内外主流先进工艺节点,如12/14/22/28nm上,均已成功通过验证测试。DDR4产品的最高速率可达3200Mbps,而LPDDR4/4X产品的最高速率可达4266Mbps。另外,近期已完成6400Mbps LPDDR5方案开发,并继续推进更高速率的DDR5方案,持续发力加速量产验证进程,展现出在高速接口IP领域的强大实力和持续创新能力。

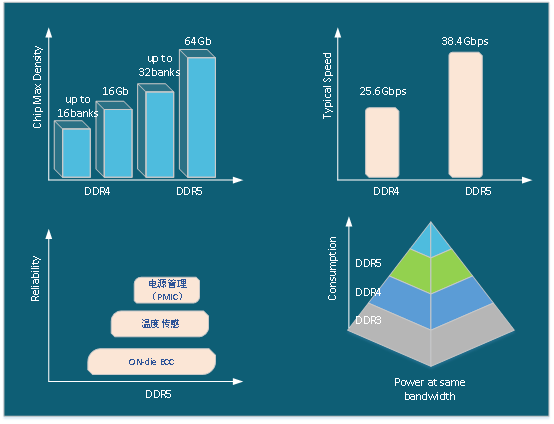

图5:牛芯半导体DDR4测试眼图

DDR5

技术突破与未来展望

值得关注的是,DDR接口技术的发展历程一直紧密跟随CPU处理器对带宽需求的步伐。然而,随着DDR5的出现,在某些应用场景中,DDR5的带宽性能超越了CPU处理器的需求。

CPU处理器的缓存体系中有个概念叫Cache line,对于X86架构的CPU,它的Cache line大小是64Bytes,在DDR4协议中支持的Burst Length是8,对于位宽64bit的总线来说,一次Burst传输刚好是64Bytes的数据,与Cache line大小一致。然而DDR5支持的Burst Length是16,对于位宽64bit的总线来说一次Burst传输将是128 Bytes的数据,两倍于Cache line大小。为了匹配这种差异,DDR5引入了sub-channel,将有效位宽64bit拆为两个sub-channel,使得每个sub-channel的Burst传输的数据匹配CPU的Cache line,最大限度的发挥两者的性能。sub-channel的设计,也可以说DDR5非常适合当今流行的多核处理器架构。

不过,尽管目前的DDR带宽已经很高,但由于现代计算机的演进出现了越来越多的多核架构,核数越来越多,因此按核数量折算之后,平均每个处理器核的带宽并没有富余,反而在当下高性能计算、数据中心、AI训练等系统中,算力增长需求远超内存带宽的增长,内存带宽依然是整个计算机体系的瓶颈。

可见即将发布的DDR6 SDRAM技术,以及更长远的未来展望,高速、高带宽内存技术的迭代与演进不会停歇,DDR内存芯片和DDR接口芯片将继续扮演着重要角色。我们有理由相信,DDR接口技术将带来更多创新,满足未来电子设备对于内存的严苛要求。

牛芯半导体也在为未来的DDR6技术进行前期的预研和准备,以确保在内存技术领域的持续领先。通过不断的技术创新和行业深耕,牛芯半导体致力于为客户提供高性能、高可靠性的DDR解决方案,助力半导体行业的可持续发展。