作为基于精简指令集原则的开源指令集架构,RISC-V经过近年来的快速发展,已经和ARM、X86呈三分天下之势。Semico Research预测,到2024年RISC-V芯片出货量将达624亿颗。RISC-V的发展也给中国芯片产业带来重要机遇。中国现已成为全球RISC-V生态社区建设中的重要力量。芯来科技是中国本土最早致力于RISC-V CPU IP的企业之一,成立以来一直专注于RISC-V CPU IP及相应平台方案的研发,成为中国本土RISC-V CPU IP的领军企业。在近日召开的第八届集微半导体大会集微通用芯片行业应用大会上,芯来科技创始人胡振波针对IP标准化与芯片产业趋势,结合中国本土市场特点,创造性地提出了“RISC-V IP 2.0模式”,进一步地丰富了中国RISC-V的发展思路。那么,“IP 2.0模式”的内涵是什么?它的提出与实施将对未来中国RISC-V起到何种促进作用?

三分天下,RISC-V快速成长

从单一走向多元,从专用走向通用,从物联市场走向高性能领域是RISC-V产业的发展主线,这一进程也从近年来RISC-V产业取得的一系列进展得到印证。从多元化应用角度看,RISC-V已经扩展到汽车、通信、机器人、ICT、电力行业等多个领域,正在加速落地生根;从软件生态角度看,2023年包括谷歌、英特尔、英伟达、高通、阿里等在内的13家企业发起了旨在加速RISC-V的软件生态建设的全球RISC-V软件生态计划RISE;从技术进步角度看,RISC-V架构正在不断优化,并与AI技术深度融合;从成本效益角度看,RISC-V的IP可以降低授权成本,这对于成本敏感的市场尤其具有吸引力。

在接受集微采访中,芯来智融半导体科技有限公司(简称芯来科技)创始人胡振波指出,RISC-V在国际上广泛进入人们视野大约是在2015年,进入中国大约是在2018年,至今不到10年时间。在这段时间里,RISC-V取得的成绩是多元的。其中最大成就是让全社会形成了一个共识,即RISC-V已经成长起来,并在人们的认识中与ARM、X86架构并列,呈现三分天下之势。这一成就的取得并不简单,它意味着从事RISC-V相关事业的人们不需再花费过多教育成本,整个社会已经认识到RISC-V行业发展的重要性。

伴随RISC-V行业的一路成长,芯来科技也在持续进步。作为最早致力于RISC-V CPU IP的中国本土企业之一,从2018年成立起,芯来科技一直专注于RISC-V CPU IP及相应平台方案的研发,伴随中国RISC-V行业的成长而成长。胡振波认为,芯来科技这些年取得的最大成就,是坚持住了作为一家RISC-V IP公司的本质,并且把握住了一个合理的发展节奏。

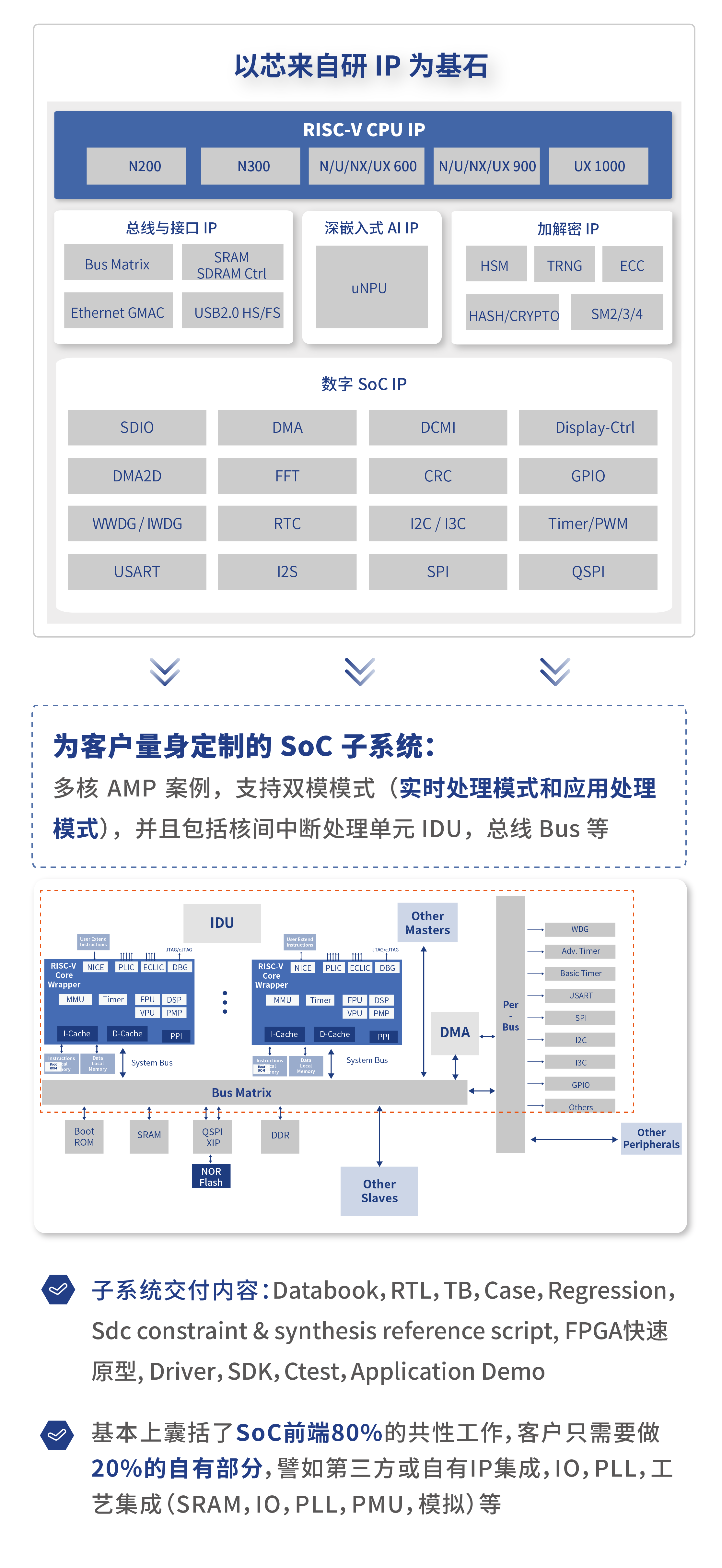

“坚持本质的核心是芯来科技积攒下了大量IP产品。作为一家CPU IP公司,IP就是核心,没有IP就失去了发展的载体。同时,芯来科技还把握住了发展的节奏,无论行业如何喧嚣,我们认识到RISC-V将有一个长期的发展趋势,始终坚持稳扎稳打、不疾不徐,保持住一致的发展节奏。通过6年耕耘,芯来科技从零开始,完全自研,打造出了N/U、NX/UX四条通用CPU IP产品线和NS、NA、NI三条专用CPU IP产品线,构建起全球最完备的RISC-V IP产品货架之一,同时也服务了大一批客户,正式授权客户超过250家,累计出货量达数亿颗。”胡振波介绍。

“随芯包”加持,IP应用更具灵活性

集成电路的成熟发展得益于IP、EDA、材料、设备等产业链的细分,正是产业细分所导致的经营效益提升,造就了当前集成电路产业快速的技术迭代与持续增长的市场规模。而IP授权模式则是产业链细分进程中的关键一环,它减轻了集成电路设计企业工作负担,将设计人员从大量的重复工作中脱离出来,对行业的发展起到举足轻重的作用。

不过采访中,胡振波将上述IP供货方式称之为“IP 1.0”模式。它的主要表现是,由不同的IP Vendor提供不同种类的标准化IP,再由芯片设计公司将不同标准化IP加以组合集成,开发形成芯片产品。处理器IP及与之密切相关的处理器指令集架构是整个集成电路产业上游最重要的核心部件,也是最为关键的底层技术。这种IP标准化与SoC集成的方法论已经深入人心,并形成了中立IP Vendor与广大SoC设计企业共存的产业格局。

但是随着行业的发展现有的IP授权1.0模式也出现了一系列问题,特别是在适应中国本土市场时,面临着一些痛点。首先就是IP的获取门槛高,对于设计公司来说,针对不同应用的不同IP都需要单独申请与单独评估,每个项目都需要单独的授权费用;其次是决策成本高,由于不同应用的不同IP都需要单独申请与单独评估,这就使得芯片项目的立项与选型决策成本增高;第三是商务法务流程长,无论是IP公司还是设计公司,每个项目的商务法务都有一个需要完成的冗长流程。这些问题是执行每个芯片项目时,都要面对的,复杂而冗长。

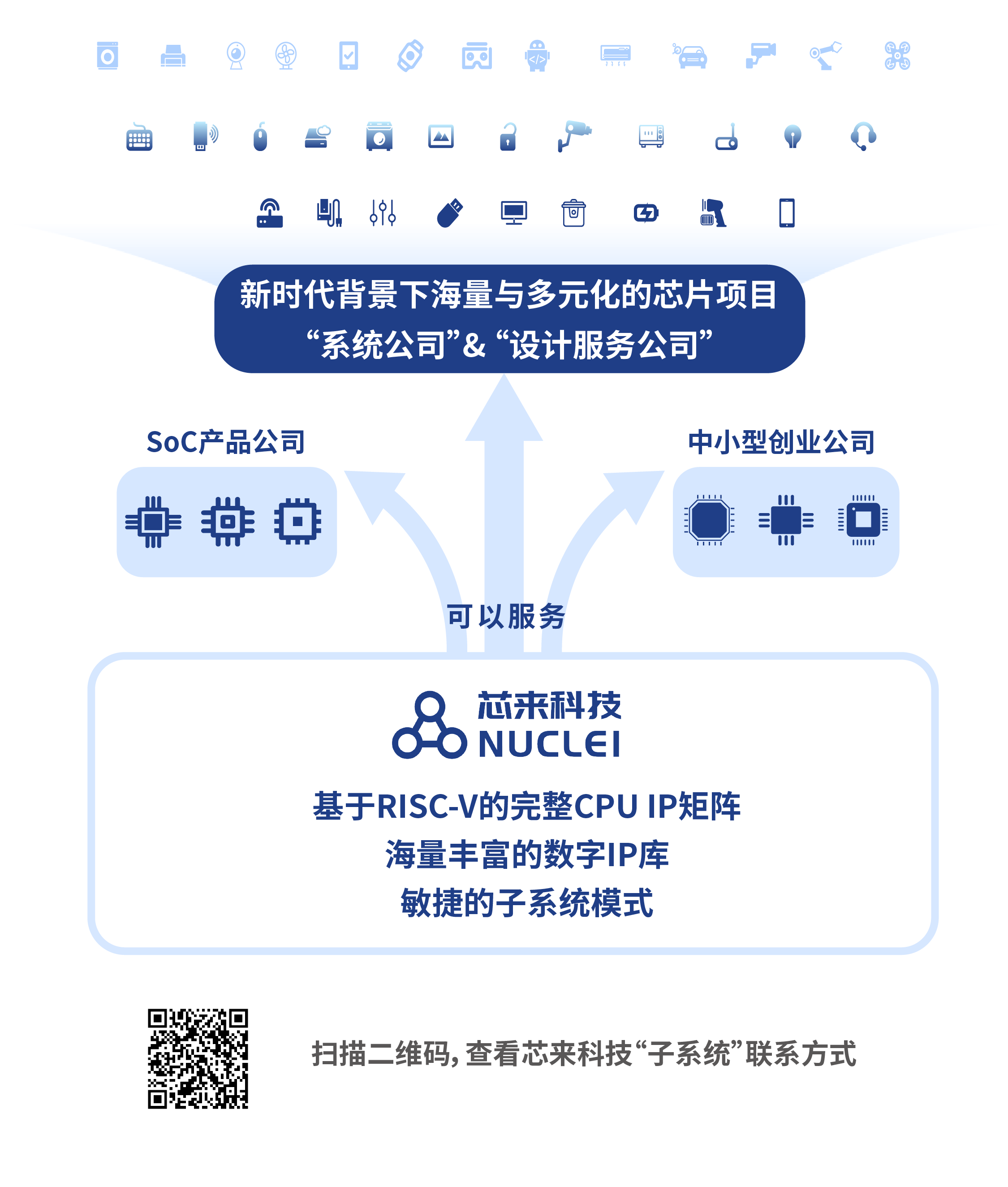

对于中国本土设计公司来说,面临的挑战还会更多。相比而言,海外芯片设计领域的业态已经趋于成熟,中国本土市场更为碎片化,项目节奏越来越快,SoC定制性与时效性强,Time-to-Market要求很高。尤其是目前本土芯片项目方普遍面临着资金紧张、时间紧张、人力不足等方面的压力。他们需要花大量精力采购或自研周边的其他IP,还需要在SoC集成与复杂验证上投入大量人力,同时SoC集成与验证周期长,时间成本高昂。

这就需要更加灵活便捷的商业模式加以解决。正是基于长期的行业经验积累,近日芯来科技全面提出一套新型的IP授权模式,称之为“RISC-V IP 2.0模式”。根据胡振波的介绍,新模式包含两方面内容。一是“随芯包”模式。其核心内容是将传统按项目授权转变为订阅模式,可大幅缩减CPU IP授权成本和授权过程,给客户带来极大的便利性和灵活性。客户可以根据自己的实际需求选择订阅内容,订阅期内可以无限次使用随芯包中的IP,无需进行任何商务法务的谈判。如果有需求可以随时对随芯包进行升级,加入更多IP产品。已购买和签订订阅合同的客户,订阅期内的IP使用无需额外付费,只需在量产后支付权利金版税即可,订阅期内实时享有IP特性和工具链的升级,以及技术支持。

“子系统”加速,为客户量身定制SoC子系统

芯来科技还推出另外一种“子系统”模式。其核心是通过SoC整体IP化的方式,降低SoC项目的设计成本。采用“子系统”模式,客户仅需要相比传统模式几分之一的预算(省钱)、投入少量的人员(省力)、极少的等待时间(省时),便可完成一颗SoC芯片的前端工作。基于“子系统”模式,芯来科技推出面向了AI、HSM和车规的垂直解决方案,可以解决80%共性问题,极大减少SoC前端设计工作量与成本。

随着越来越多系统厂商开始自研芯片,定制化的SoC子系统服务被越来越多IP公司所重视。Arm此前便推出面向服务器与移动终端的计算子系统(CSS)。胡振波强调,芯来科技“子系统”模式更加强调量身定制的特性。芯来科技可以根据用户的需求,以自研积累的通用SoC IP为基石,根据客户需求提供量身定制的SoC子系统服务,甚至是可以以星期为单位进行交付,真正意义上为用户带来颠覆式的时间与人力成本下降。

赋能IC产业,“RISC-V IP 2.0模式”提供新动力

结合CPU IP随芯包模式与子系统解决方案,胡振波将之称为“RISC-V IP2.0模式”。通过大幅缩减CPU IP的授权成本和大幅降低SoC前端精力和成本,芯来科技将助力本土设计公司更高效地完成CPU IP的授权过程,加速本土芯片设计企业产品上市进程。