当今设计流程正在保持极速演化并推动我们实现高度优化的 IC、PCB 和系统,实现全球化的创新。目前,通过在设计探索和验证过程中更早地应用分析,我们已经成功实现了复杂多物理场分析和多领域协同优化。然而,日益增加的设计复杂性,使得传统的分析方法正接近瓶颈,转而通过机器学习(ML)和 AI 支持的流程将逐步登上未来发展的舞台。

这听起来似乎有点夸张,但如果应用得当,ML 技术将发挥非常强大的作用,而电子行业永远不缺的恰巧就是将设计数据“喂”给机器学习。当然,关键在于我们需要发展出更成熟的方法,可以有效地将 ML 与数据相结合,从而实现最大化的效益。

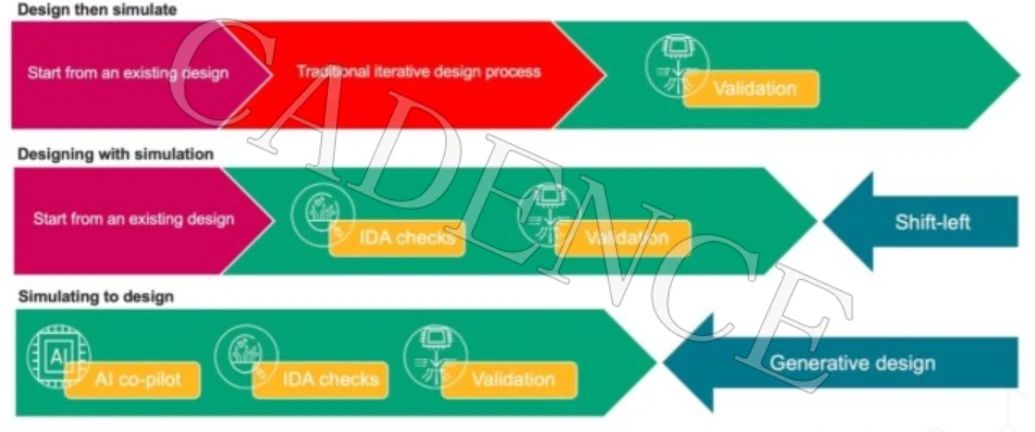

具体到芯片设计流程,目前从设计到签核大致需要经过下述步骤:首先创建设计,之后通过仿真确定是否符合设计标准,如果不符合则进行调整并迭代。这套流程的确可以实打实地看到结果,然而却面临着如下挑战:

1.设计复杂性的不断增加。

2.多领域的协同优化。我们发现必须将 IC、电路板和系统作为一个整体来开发,才能真正实现优化,这又进一步增加了复杂性。

3.应用于单一设计领域的物理限制也越来越多地影响到其他领域。

这些挑战使得传统设计方法的短板开始显现,设计师们需要无休止地在探索流程和分析工具间来回切换以检测他们的设计。所有的这一切都让设计中的多问题协同优化寸步难行,例如热效应对 IR drop(直流压降)的影响或不同封装方式对信号完整性的影响。

为了解决这些问题,EDA 厂商正在努力打破“先设计再仿真”的传统方法,为设计师在流程更早期便提供设计分析能力——也就是通常所说的“分析左移”或更学术的说法“设计中分析”。这使得设计师能够进行更多的系统设计和协同优化,例如分析信号穿过 SerDes 通信通道时的完整性,这个过程包括信号从发射器 IC 芯片经过其封装,穿过 PCB,到达接收器 IC 的封装,最后进入接收器的芯片。

“分析左移”的方法让设计师能够更系统地去思考,强大的设计工具可以帮助设计师识别跨域约束的冲突,安全且及时地发现优化机会。现在的挑战是如何有效地探索这些扩展的设计空间,特别是习惯在单一领域(比如 IC 或 PCB)工作的设计师,他们更需要适应并学习多领域协同优化。

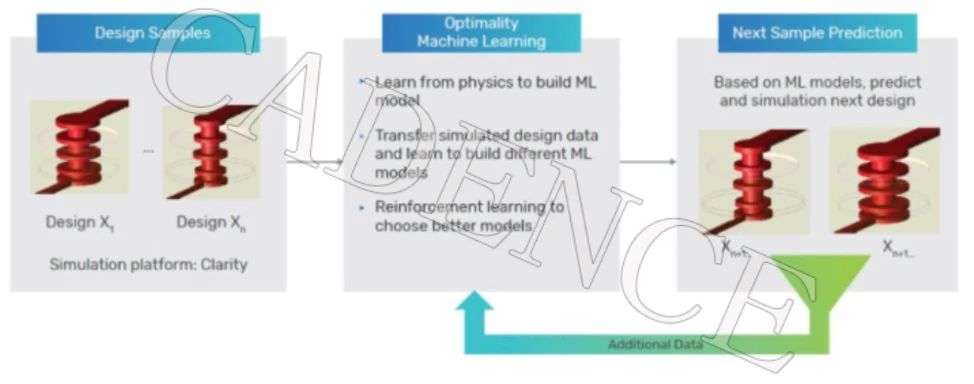

此时 ML 技术终于迎来大展身手的舞台。尤其是现在大火的生成式 AI 技术,它可以基于最初在多个候选设计的物理基础上训练模型,产生设计选项,例如 IC 中连接层的过孔。对候选参数进行仿真时,生成的数据将被反馈给模型,用于强化学习。模型会保持不断更新,并不断生成更好的候选设计,反过来推动模型的进一步演化。值得一提的是,Cadence 在 Optimality Intelligent System Explorer 工具中实现了上述流程,帮助设计师解决了在大幅扩展的系统设计空间中面临的“选择困难症”。

将 ML 应用于电子设计的下一个方向,很可能会涉及设计师和 EDA 工具供应商所拥有的大量设计数据集,通过这些海量的数据,来提取出代表设计成功或失败警告的模式。此时设计将变成一种协同工作,由设计师和 AI 助手携手在已知模式的限制下共同探索新的设计空间。在新场景下,早期设计探索可能不再由仿真工具驱动,而是更依赖于辅助应用程序,AI 助手不会简单地告诉设计师“不要做”,而是会根据数据分析,指出哪些特征可能导致失败,引导设计师做出更好的选择。

虽然在实现这样的联合试点工作之前,我们还有很长的路要走。但 Cadence 已建立起 Cadence Joint Enterprise Data and AI(JedAI)Platform,利用数据库基础设施、工具和路线图、经验和见解,将 ML 和 AI 的力量应用于电子设计。Cadence 将助力设计师们始终走在全球创新前沿,不断推动创新的边界!