尽管当前SoC日渐复杂,多核多功能,低功耗和高性能依旧是设计的风向标。对于内存接口而言,更高密度和更低功耗位列评估内存解决方案的重要指标,DDR5、LPDDR5、GDDR6以及HBM2E等新一代的内存接口技术也因此逐渐成为市场主流。即使面对DRAM市场周期波动,以及存储大厂库存积压和缩减成本的压力,内存DRAM的新势力技术依旧火热,甚至还有加大投资的势头。加上生成式AI应用、高算力芯片的带动作用,更高带宽的DRAM接口保持强势增长。

AI大模型时代来临,推动DDR5技术加速普及

JEDEC(固态技术协会)将DDR5描述为一种“具备革命意义”的内存架构,迎合AI、云计算、物联网等新技术带来的存储和数据传输需求。相比DDR4,DDR5提供了更高的传输速率以及更高的带宽,从而将内存容量进一步扩大。同时,通过采用更低的电压以及先进的传输效率,DDR5也为复杂SoC,高性能计算提供了基础条件。

DDR5首先解决的是速度问题,6400Mbps的传输速度将单个DQ的速度提高一倍(目前业内最高的速率已达到8400Mbps)。与之相应,速度提高也带来了更高的密度。DDR5内存支持更高的内存密度,这意味着在相同的物理空间内,可以容纳更多的内存,这对于需要处理大型数据集或运行内存密集型应用程序的用户来说是非常有益的。相比DDR4,DDR5的容量提高了4倍,达到64Gb。每个通道的突发长度已从8增加到16,这意味着比起DDR4, DDR5 将能够在相同的时间内执行两个 64 字节操作。DDR5具有16n预取架构,这使其具有更高的速度。另外,DDR5引入更多的Training训练种类,多tap DFE的加入,可以解决传输链路上的ISI问题。

在DIMM方面,DDR中提供了电源管理电路,PMIC的加入大大提高了电源完整性。在此条件下,电压可降至1.1V,低于DDR4。而通过PMIC的分配,可以减少噪音和串扰等问题,也为改善信号完整性提供了一定助力。

降低功耗对于设备节能和电池寿命延长尤为重要。DDR5加入了双通道的支持,两个40bit的通道能有效提升内存访问性能,同时也为速度提升提供保障。具体到细节,DDR5在DIMM会引入更多的温度传感器,边带信号升级为I3C,多重升级下,降低了速率容量提升所引起的设计难度。

基于DDR5为传输速率、带宽、容量等方面带来的种种优势,无论是 PC、笔记本电脑还是人工智能,各行业和应用都正在加速向 DDR5新纪元迈进。生成式 AI 市场蓬勃发展,用于大模型应用的 AI 服务器也将大力推动对DDR5的需求。

LPDDR5技术:更高带宽、更高速度、更低功耗

2019年2月,JEDEC发布了LPDDR5 标准,相对上一代的LPDDR4x,LPDDR5在速率、功耗和性能等方面均实现了跨越性的升级换代。LPDDR5采用3200MHz的时钟频率,就数据率而言,速度达到6400Mbps,相比LPDDR4X提高1.5倍,而LPDDR5X和LPDDR5T甚至可以分别达到8500Mbps和9600Mbps。LPDDR5虽然采用了单16bit通道,但是通道本身的存储体量已增加2倍,且可支持多bank group的模式,进一步提升数据带宽。

在功耗方面,由于电压已降低到0.5V,并且LPDDR5具有DVFS、深度睡眠模式、DQ复制和Write X等新节能功能,LPDDR5通过使用动态电压调节 DVFS 功能,使得功耗成功降低45%,实现更多节省。此时,存储器、控制器可以在通道待机期间降低 DRAM 的频率和电压。LPDDR5通过DVS支持两种内核和I/O电压,高频应用下分别采用1.05V和0.5V运行电压,在低频应用下分别运行0.9V和0.3V电压。另外,通过采用先进的可扩展CA/CK时钟结构,可以减轻SoC设计者的时序Signoff压力。而Write X的功能加入,则允许将特定的全零模式转变成连续的存储器位置,而无需切换通道上的 DQ,即可将功耗进一步降低。

图表1 LPDDR5速度比较

图表2 DDR5/LPDDR5技术比较

LPDDR5的应用上,率先火热的是智能手机市场,同步也伴随着在平板电脑应用的风生水起。目前在汽车智能化和AI方面,越来越多的LPDDR5技术将被采用。11月28日,长鑫存储正式推出LPDDR5系列产品,包括12Gb的LPDDR5颗粒,POP封装的12GB LPDDR5芯片及DSC封装的6GB LPDDR5芯片。国产LPDDR5颗粒将迎来新的一波中高端移动设备市场浪潮。

GDDR6/HBM技术,专门应用下的专业选择

当下电脑游戏火爆,推动电脑游戏对显卡GPU产生高速数据交互需求,而且随着显示技术日新月异,更高帧率、更宽画幅的游戏也迫切需要更高带宽和更频繁的交互。因此,另一个DDR分支——GDDR应势而生,GDDR适合具有高带宽需求的计算领域,例如图形相关计算、数据中心和AI等。

一开始GDDR初代与DDR并没有很大区别,但在市场和成本的影响下,二者功能逐渐分道扬镳。此后,疯狂提高的带宽需求迫使GDDR技术不断发展,256-bit的GDDR6带宽已经可以达到768GB/s。显存可以直接贴片在显卡上,弱化了走线、信号传输延迟等影响。因此,GDDR也出现了和DDR/LPDDR不同的技术路线:一方面,采用高prefetch, 这样就可以在每个周期(每个通道)中获取64字节(512位)的数据;另一方面,采用提高burst length方法,GDDR6突发长度为16字节(与DDR5一样),这使得内存每次传输最多可获取64B高速缓存行。GDDR6可以在两个独立的通道中获取与GDDR5X相同数量的数据, 同时还将密度提高到16Gb。

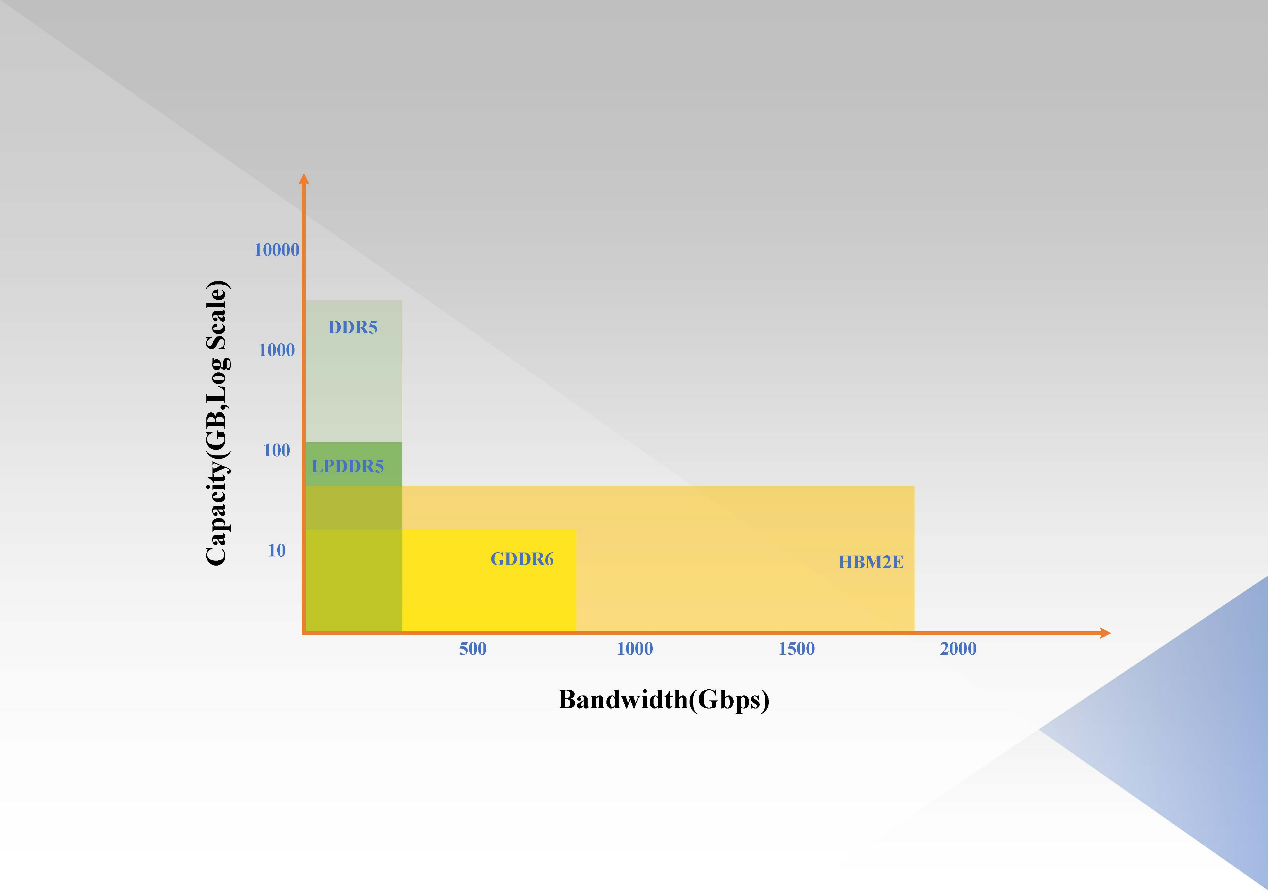

图表3 LPDDR5/DDR5/GDDR6/HBM技术比较

随着应用的复杂程度提升,处理器和存储的交换也愈发频繁,急需一种提供高带宽高位宽的技术解决能耗和拥挤的问题,HBM(High Bandwidth Memory )应运而生。与GDDR5相比,HBM如同高速公路,可获得更高的带宽,而尺寸却小得多。HBM是一个从传统2D向立体3D发展的代表产品,开启了DRAM 3D化道路。HBM采用低速时钟,并通过大量总线来弥补带宽的损失,使宽度最多可达4096位。相比上述的DDR技术,HBM具有更高带宽,更高位宽,更低功耗,更小外形的特点。HBM2E中,时钟和选通以相同频率运行,最高可达1.8 GHz,以实现最低延迟解决方案。HBM3 将传统时钟信号从主机去耦到器件和数据选通信号,以此来更改时钟架构,WDQS 和 RDQS最大速率为3.2 GHz,可实现高达6.4 Gbps 的数据传输速率。

图表 4先进DDR技术带宽容量比较

作为SoC芯片重要的组成部分,DDR主要负责硬盘、主板、显卡等硬件与处理器之间的数据交换。当前,追求更快速率、更高带宽、更大容量、更低功耗的DDR内存技术已成为不可逆转的发展趋势,DDR模块的设计难度随之增大,因此,来自IP厂商成熟可靠的DDR IP产品成为芯片设计企业的不二选择。

根据研究机构 IPnest 数据,2022年全球半导体IP市场规模达到66.7 亿美元,同比增长20.2%。IPnest 预计,到2025年半导体IP市场规模将超过100亿美元,2021-2026 年的复合年增长率为16.7%。目前,中国半导体IP市场增速与全球半导体 IP市场基本持平,市场潜力巨大。

随着AI、汽车智能化、Chiplet等新技术趋势为IP产业带来新变量,接口IP作为半导体IP最具潜力的细分品类,赋予了国产厂商更多机会。

牛芯半导体DDR4/LPDDR4多客户量产追单,IP成熟稳定

牛芯半导体致力于半导体接口IP的开发和授权,并基于接口技术提供相关整体解决方案。牛芯半导体与多个Foundry厂合作,在主流先进/成熟工艺布局SerDes、DDR等中高端接口IP,依靠细分领域的技术积累,牛芯半导体自主研发的IP产品和相关服务已获得累计超百家客户使用。

在DDR IP布局上, 牛芯半导体能提供成熟稳定的DDR3/3L/4 和LPDDR2/3/4/4X MC+DDR完整解决方案,DDR4速率支持3200Mbps,LPDDR4/4X支持4266Mbps。除了在国内外主流先进工艺节点12/22/28nm均取得成功的验证测试结果,同时也面向国内多家客户实现芯片稳定量产。

在与某客户的合作案例中,牛芯半导体的DDR3/4 LPDDR4 Combo IP充分利用12nm的平台优势,功耗业内领先,访问效率优势明显,并支持Wire-Bonding封装,以及更低层数的PCB设计。更值得一提的是,DDR IP在HTOL、温循、电源拉偏等条件下仍可以稳定工作,展现出高度的可靠性。据牛芯半导体技术支持工程师介绍,牛芯半导体DDR产品采用可靠稳定的训练算法,能改善不同DDR拓扑和环境所引起的不稳定。其中,高速DDR I/O的设计也得益于牛芯半导体在SerDes高速接口方面的长期积累,SerDes接口中所使用的部分模块为DDR设计提供了借鉴,两者呈现相辅相成的特点。

牛芯半导体DDR5/LPDDR5保持优势,多工艺平台百花齐放

目前,牛芯半导体已在多个工艺节点下布局DDR5/LPDDR5产品,涵盖先进工艺以及国产工艺,基于数字架构的独特设计,使得DDR PHY更易在不同工艺间迁移,在带宽和时延的性能平衡以及面积和低功耗的表现上均达到业界一流水平。同时,在开发上更注重国产DRAM颗粒的支持,并对此进行特别调试优化以增加鲁棒性,使客户在颗粒供应上拥有更全面的选择。

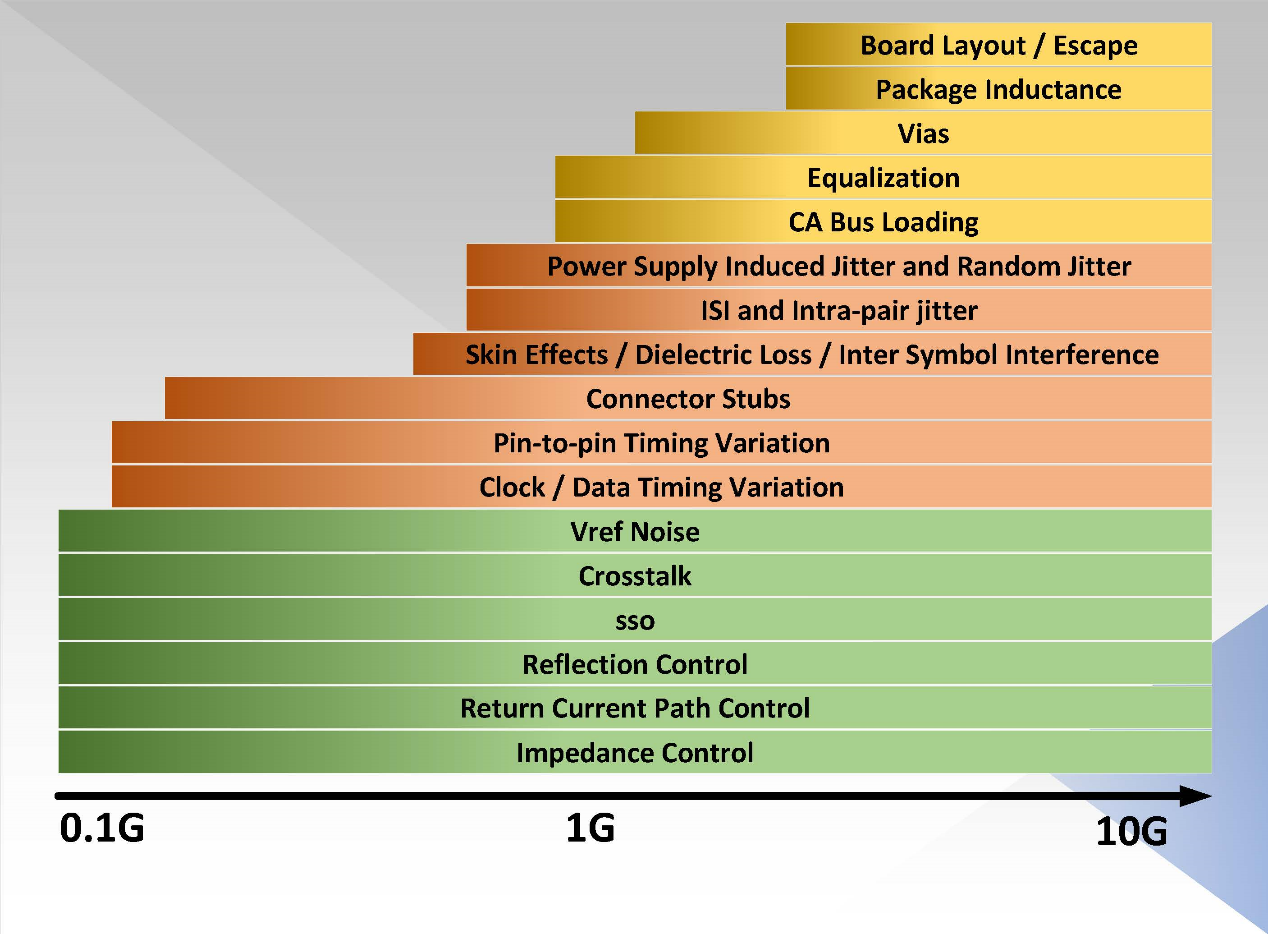

为了充分发挥 DDR5/LPDDR5的性能,必须在芯片、封装、 PCB 等系统关键点上进行兼顾电源影响的信号完整性分析。牛芯半导体为客户量身定制信号完整性和电源完整性方案,围绕DDR5/LPDDR5,提供针对信号衰减和电源对信号影响的快速检查,基于在电源网络和信号网络以及高速I/O的丰富建模经验,能够对多个信号网络和电源网络时序进行仿真。

图表 5信号完整性影响因素

凭借高性能、低功耗的特点,牛芯半导体多款IP产品技术指标居行业领先,广泛应用于消费电子、网络通信、数据存储、高性能计算、物联网、人工智能、汽车电子、工业控制、医疗电子等领域。未来,面对广阔的市场,牛芯半导体将凭借其多年积累的芯片设计和量产经验,努力把握时代机遇,持续专注IP国产化与产业应用需求,通过接口IP的自主知识产权研发和创新,为IC设计产业不断注入“芯”活力。