近日,为填补国内集成电路市场上产业化CMP建模工具的空白,满足芯片设计公司和晶圆制造厂的需求,广立微正式推出CMP EXPLORER(简称“CMPEXP”)工具,保障芯片的可制造性和成品率,解决行业的痛点。

化学机械抛光(即Chemical Mechanical Planarization CMP)是集成电路制造工艺中的关键环节,结合了化学反应和机械研磨来实现硅片表面的高度平坦化。

随着集成电路制造工艺的演进迭代,纳米器件尺寸不断缩小,再加上集成程度提高及工艺层级越来越多,芯片在制造各阶段的表面平坦度严重影响产品成品率及性能,其影响通过多层叠加和版图特征效应更加突出,可谓“差之毫厘,谬以千里”。如何实现CMP步骤的仿真、建模和优化,一直是保障芯片成品率的重要挑战。

即便在芯片设计时严格遵守了设计规则,对于一些工艺较敏感的设计Pattern,仍有可能在CMP阶段形成碟型凹陷(Dishing)、介质腐蚀(Erosion)和金属厚度波动等缺陷,从而造成互连线电阻、电容波动,甚至金属互连短路和开路。这样一来,后续制造步骤中的工艺窗口变窄,任何工艺上的小波动能造成成品率问题,因此,可制造性设计(Design for Manufacturing DFM)的角色更为重要,通过针对CMP步骤精准仿真和建模,可以提前找出和预防CMP相关的芯片设计问题。

进军DFM

作为广立微进军DFM领域的首款EDA工具,其可依据CMP工艺后的各测试结构膜厚和表面形貌数据以及CMP工艺参数,建立CMP模型。

设计人员可在芯片流片前,使用软件内的CMP模型对版图进行CMP仿真并进行可制造性分析,对识别出的CMP工艺热点提前进行修复,从而实现在设计端成品率优化,减少了设计端的成品率风险,有效降低芯片研发成本。

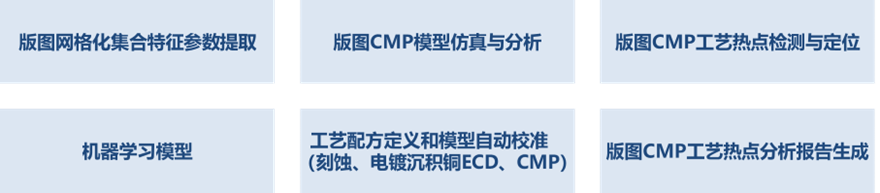

CMPEXP主要功能

目前,广立微的CMPEXP工具已完成了第二阶段的开发,实现了业界广泛使用的Cu CMP仿真与热点检查流程的所有功能,软件的成熟度也已达到商用水平,其中工具特点包括:

考虑了接触力学等物理和相关化学原理,同时结合快速傅里叶变换等数学手段,提供了高准确性,鲁棒性和泛化性的CMP模型。

采用了高效的分布式并行计算架构,有效地提升了模型校准和仿真效率。

集成了先进的模型校准算法,大大地缩短了模型校准时间周期并有效提升了校准成功率。

采用数据表,散点图,折线图,柱状图,热力图,3D图多种手段准确直观地展示模型校准,仿真与热点检测结果。

完善产品矩阵

这次CMPEXP EDA工具的推出,进一步完善了广立微的制造类EDA的产品矩阵,同时与广立微现有的成品率提升方案相互协同和补充,为集成电路企业提供更完备的解决方案,助力行业发展。