最近在与手机终端客户交流过程中,发现客户对于射频前端芯片的理解已经越来越深入:从最早的只把射频芯片当成一个黑盒子,到对PA等模块架构特点熟悉,再到对放大原理深入了解,国内手机终端公司逐渐把射频芯片从“用得了”,到“用的好”。

在对射频芯片的工作原理了解清楚之后,一些手机终端公司逐渐向芯片的更深层次:半导体器件层级研究。考虑研究深入的器件物理机理,对应用中看到的问题加以解释。

芯片之所以是芯片,就是因为半导体技术;芯片系统与板级系统最大的区别,也就是因为使用到了半导体物理器件。半导体器件是芯片公司的根基所在,手机终端公司对于半导体器件的研究,让我们这些芯片公司的“硅农”们感受到同道相益,备受鼓舞。

不过我们也发现,即使对于芯片公司或芯片工程师来说,“半导体物理”都是一个让人望而生畏的词。由于半导体物理太过晦涩难懂,很多的集成电路设计类专业甚至不再教授此课程;即使对于半导体专业的学生来说,学校里的“半导体物理”、“半导体器件”课程也常常成为学生时代的心理阴影,以至于工作之后再也不想谈及。

于是,我们就想梳理出一份材料,一起就射频芯片中常见的半导体器件做一个讨论。

半导体工艺简介

什么是半导体

在半导体被发现之前,人们认为世界上的材料根据导电性分类只可以被分为“导电”和“不导电(绝缘)”两种。按分类方法中的“相互独立、完全穷尽”的原则看,这是对世界上材料非常完美的分类方法,那为什么还会出现“半导体”这一分类呢?

一些文献中将“半导体”定义为“导电性能介于导体和绝缘体之间的材料”,准确来讲,半导体材料并不是导电的性能处于二者之中,而是导电特性可以在二者之间可控切换。这种导电特性可以在导体与绝缘体之间可控切换的材料,被称为半导体材料。

半导体现象的首次被发现要追溯到近200年前的1833年,电子之父法拉第发现硫化银的电阻随温度变化特性不同于一般金属,温度可以实现对硫化银材料导电性的可控,这是人类首次观察到半导体现象。

在1833至1945年这100多年时间里,物理学家对这一现象进行了深入研究。20世纪初的物理学革命为半导体科技奠定了坚实的理论基础,而材料生长技术为半导体科技奠定了实现中的物质基础。

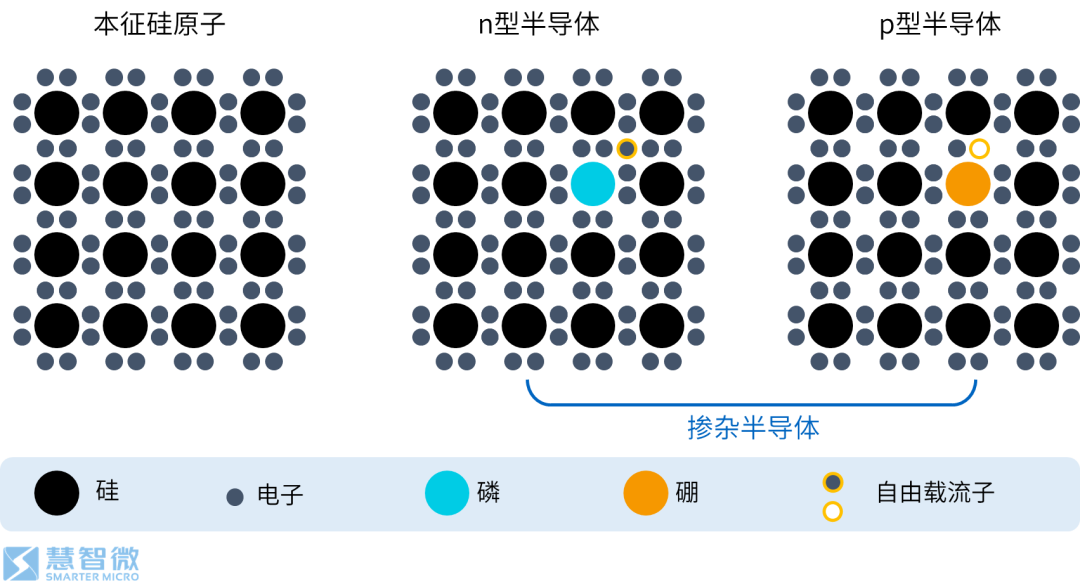

掺杂:半导体材料的实现基础

半导体导电可控特性的实现是通过“掺杂(Doping)”来实现。

以硅原子为例,每个硅原子最外层有4个电子,在本征硅材料中,每个硅原子与周围的4个硅原子形成共价结合的稳定结构,从而没有可自由流动的自由载流子,不能形成电流。

这时,如果对本征硅材料进行掺杂,如果加入最外层有5个电子的磷元素,这时在形成4个共价键之外,还会多出一个自由移动的电子,这个电子就是一个自由载流子,当加上电压之后,掺杂材料就可以导电。自由移动的电子是半导体材料中的第一种载流子。

同理,如果掺杂材料为最外层只有3个电子的硼元素,这时会出现一个电子的空缺,电子在不断填满这个空缺的过程中,也可以使材料导电。由于电子不断填充这个空缺的过程不易描述,人们就发明了一个新的表征空缺的方式,即定义一种新的载流子来表示这个空缺,这种新的载流子就是半导体中的第二种自由载流子:空穴。

半导体的掺杂工艺实现了对半导体内自由载流子的控制。

p-n结:简单的半导体器件

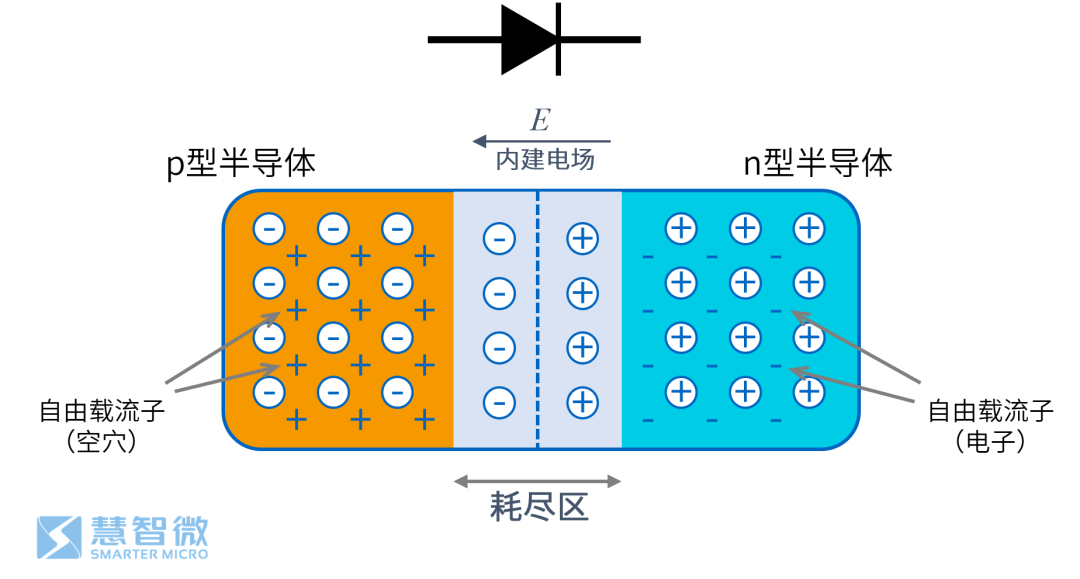

图:p-n结的基本结构

利用半导体的掺杂特性,就可以设计出简单的半导体器件:p-n结。p-n结英文名称是p-n Junction,因为有正负两个端口,所以又称为p-n结二极管。

p-n结是在同一衬底上同时进行p型和n型掺杂,并使之交界,这样在二者交界处就形成耗尽区(也叫空间电荷区),从而形成p-n结。

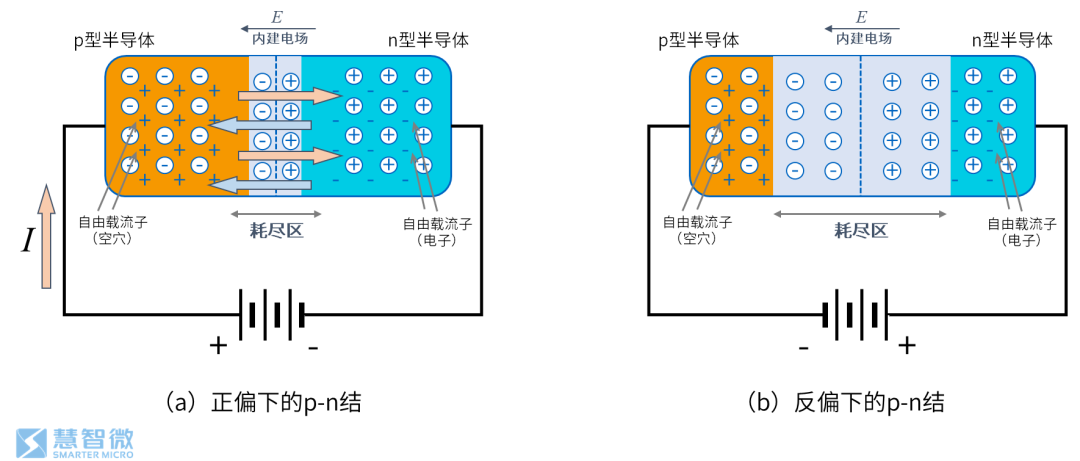

p-n结的一个重要特性就是单向导电特性。当p型半导体侧加入正电压时,p型半导体中的空穴在外加电场作用下向右侧移动。当外加电场大于p-n结的内建电场时,空穴就会跨越过耗尽区,从而进入n型半导体区,之后在电场作用下进入电源负极,形成电流。

当n型半导体侧加入正电压时,n型半导体中的自由载流子电子向右侧移动,拉大内建电场宽度,使自由载流子更难跨越耗尽区,无法形成电流。

图:正偏及反偏下的p-n结

从“晶体管”开始,直到改变世界

只是用p-n结二极管,还不足以设计集成电路。

在半导体物理的基本原理被人类掌握之后,人类就开始用半导体材料设计制造一些特殊器件。比如:

利用半导体导电性能与温度之间的关系,可以设计出热敏电阻,来感知温度变化;

利用有些半导体导电性能与光照之间的关系,可以设计出光敏电阻,来感知光的变化;

利用有些半导体光电转换特性,可以实现电能和光能的相互转化,设计出发光器件,或者设计出光伏发电器件;

虽然利用半导体材料“导电性能可控”这一特性,可以在很多领域设计出重要应用的器件。不过这个时期的半导体还是很难和之后改变世界的“集成电路”联系起来。真正建立起“半导体材料”与“集成电路”之间联系的,是1945年被发明的“晶体管”。

早在1899年,人类就实现了无线电信号的跨英吉利海峡穿越。但在晶体管被发明之前,电子电路系统一般由真空电子管设计。真空电子管体积大、功耗大、发热厉害、寿命短,并且需要高压电源,所以真空电子管所设计的电路一般只用在政府、军事部门中。真空管极大地限制了电路系统的大规模应用。

图:20世纪初,RCA公司采用电子管设计的放大器

为了克服真空电子管的局限性,第二次世界大战后,贝尔实验室加紧研究,探讨用半导体材料制作放大器件的可能性。

1945年秋天,贝尔实验室成立了以肖克莱为首的半导体研究小组,成员有布拉顿、巴丁等人。他们发现,在锗片的底面接上电极,在另一面插上细针并通上电流,然后让另一根细针靠近及接触它,并通上微弱的电流,这样就会使原来的电流产生很大的变化。

微弱电流少量的变化会对另外的电流产生很大的影响,这就是 “放大” 作用。利用这种特性,半导体器件也就可以被用于制作放大器。

在为这种器件命名时,布拉顿想到它的电阻变换特性,于是取名为Trans-resistor(转换电阻),后来缩写为Transistor,中文译名就是晶体管。1956年,肖克莱、巴丁、布拉顿三人,因发明半导体晶体管同时荣获诺贝尔物理学奖。

图:半导体晶体管的发明者,左起:布拉顿,肖克莱,巴丁

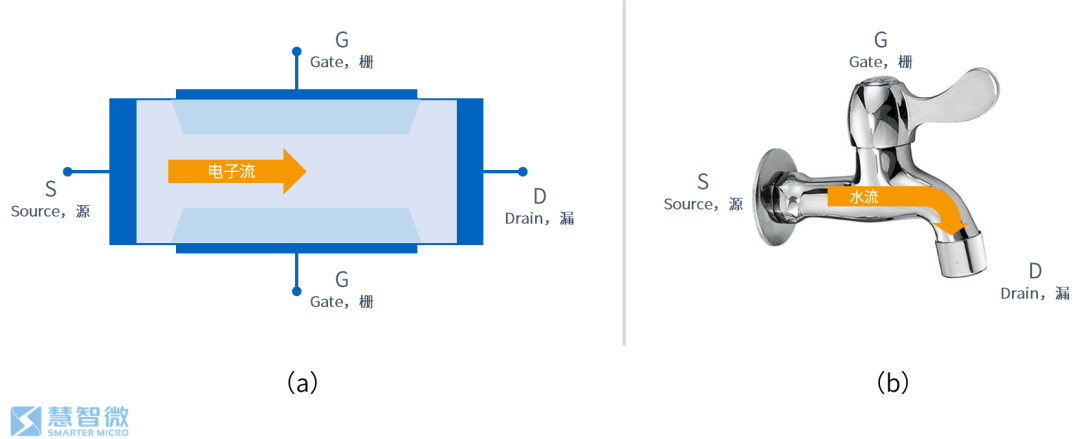

在直观理解上,可以将晶体管理解成一个水龙头:

晶体管一共有三个极,对于FET器件,一般称为源、漏、栅(S、D、G),对应水龙头的进水口、出水口、龙头把手;

晶体管源极(Source)流入电子,对应水龙头进水中流入水源;

栅极(Gate)是晶体管的核心,控制电流的大小,对应于龙头把手是水龙头的核心,决定水流的强弱;

图:典型的晶体管构造(JFET),及与水龙头的等效

基于以上原理,晶体管就可以实现信号的放大。即在栅极加一个微小信号,只要能控制住晶体管漏极到源极这个通道的通断,就可以控制漏源之间电流的大小。

晶体管还可以实现数字电路里“0”、“1”基本信号的表征。比如可以定义“水龙头”打开状态为“1”,关闭状态为“0”。成千上万个“水龙头”放在一起,就可以进行数字逻辑运算。

晶体管(Transistor)是集成电路领域中最为重要的基本器件,没有之一。有了这个基本器件,才有了现在改变世界的集成电路。我们经常看到的FET、HBT、pHEMT等器件名称中的最后一个字母“T”,均是“Transistor”的缩写。

在半导体器件里,晶体管也有多种变形,材料也多种多样,一些缩写也让人眼花缭乱。不过万变不离其宗,只要找到晶体管中水龙头的“进水口”和“出水口”,理解清楚“龙头把手”的工作原理,就可以将这种类型晶体管分析清楚。

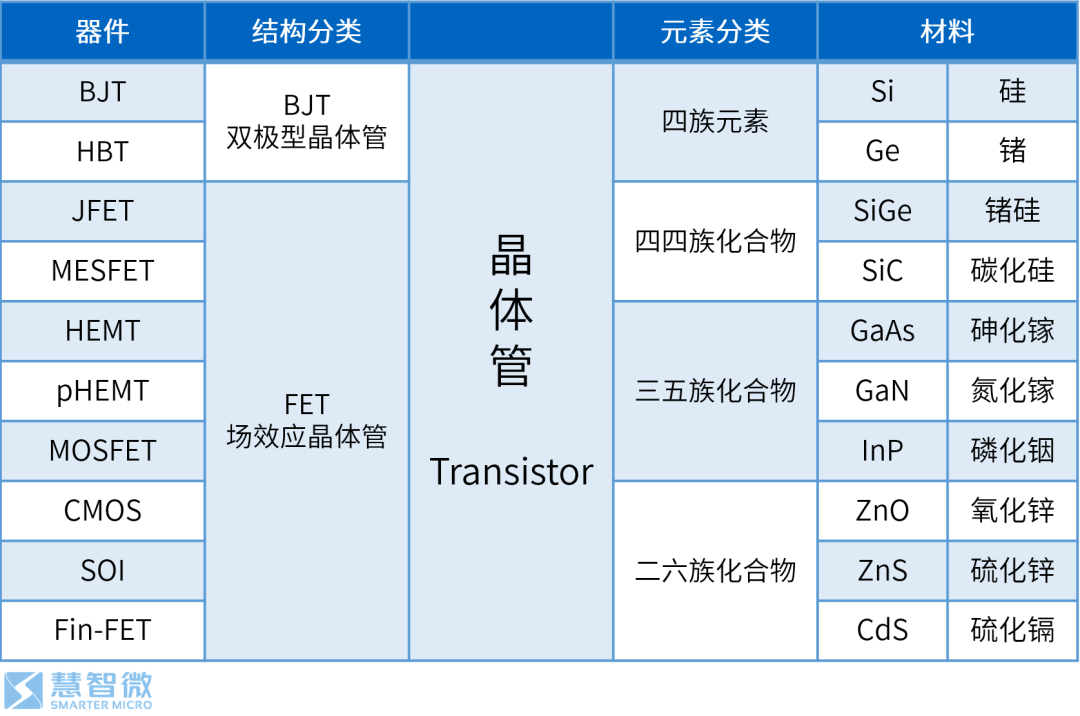

晶体管的分类

过去近100年,半导体晶体管的发展过程中,先驱科学家和工程师们不断尝试各种器件结构与器件材料,来满足不同领域集成电路特性的需求。产生出各种各样的半导体器件。

半导体本来就抽象、难以捉摸,纷杂的名称和简称也使得半导体更加高深莫测,给非半导体出身的电子行业从业者带来不少的困扰。

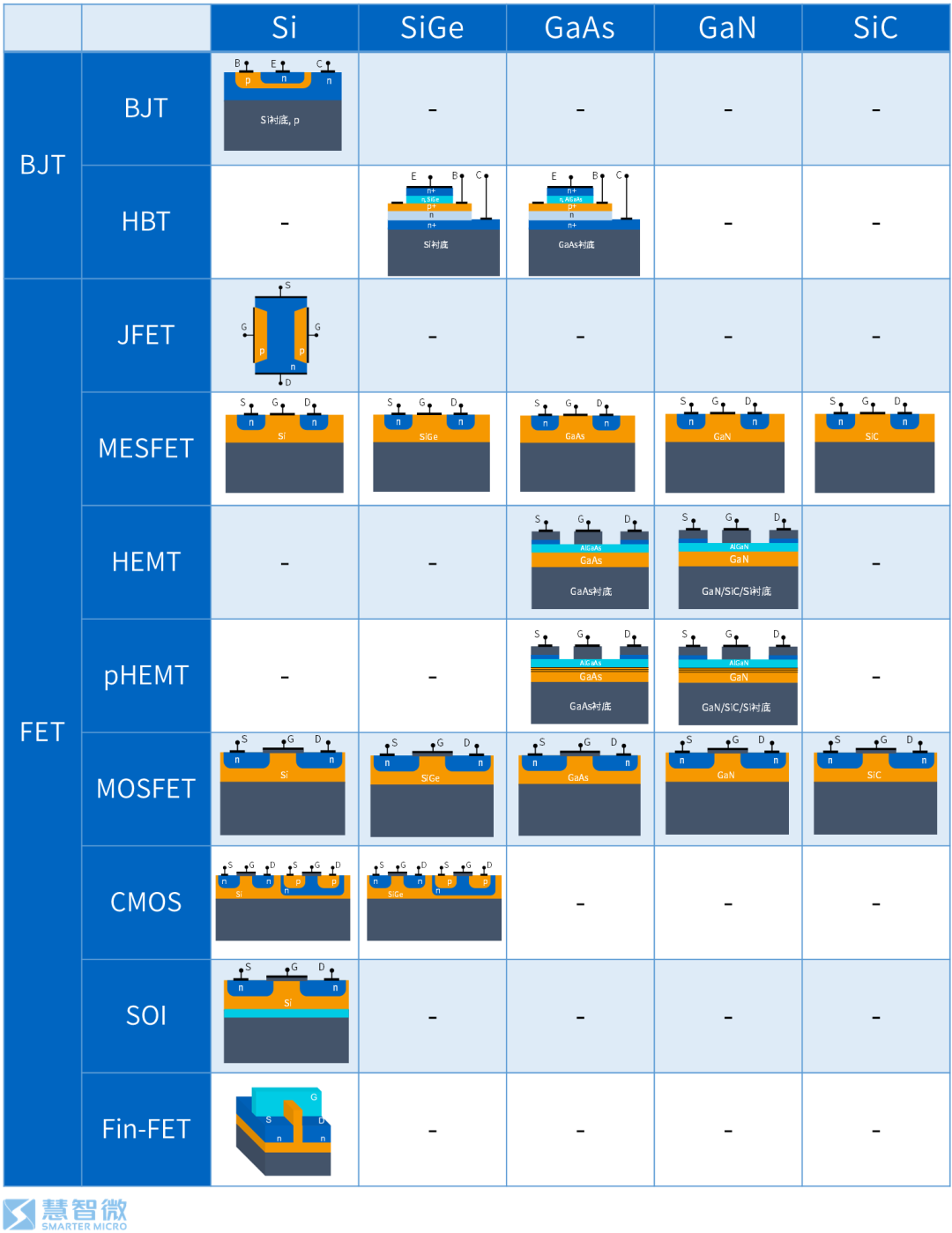

晶体管的分类主要可以从两个方面下手理解,分别为器件结构,和器件材料。以下为常见的结构和材料类型。

晶体管的材料和结构互为独立,理论上可自由组合。比如可以设计在硅基的BJT器件,也可以设计在砷化镓基的BJT器件。

对一个器件的准确描述,应该将材料与器件种类同时说明,比如对于5G手机射频PA中使用的HBT器件,准确名称应该是GaAs HBT器件。不过由于大家平时工作中的约定俗成,叫法经常加以简化。

比如在手机射频领域,大家一般用HBT,或者GaAs来简称GaAs HBT;在电源控制领域,大家用SiC来简称SiC MOSFET,用GaN来简称GaN FET类器件。这种简称在某个细分行业领域是有效的,但在跨出本行业交流时可能会引起误解,必要时需要加以注意。

以结构分类半导体

从结构上区分,半导体器件主要分为BJT和FET两种类型。

BJT的全称是是Bipolar Junction Transistor,双极型晶体管。FET的全称是Field Effect Transistor,场效应晶体管。二者都可以实现晶体管的放大特性。

BJT器件

基本结构

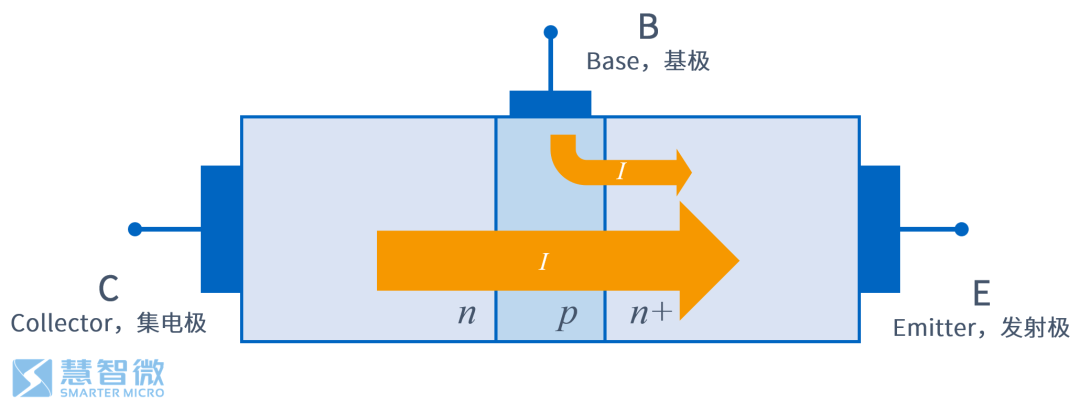

BJT器件由两个背靠背的p-n结构成。由于用于电流传输的p-n结包含电子与空穴两种载流子,所以BJT器件取名为“Bipolar(双向/双极)”Junction Transistor。

虽然BJT由两个p-n结构成,但不是任意两个背靠背的p-n结二极管都可以构成BJT。BJT器件对于各区的掺杂浓度以及厚度有着精确的要求。BJT器件中发射极需要重掺杂,基极需要较重掺杂,并且宽度极薄,以使大量的电子与空穴可以穿越。

图:BJT器件的基本结构(npn管为例)

BJT器件制备

在集成电路制备中,BJT器件先通过在n型外延中形成p型扩散,形成基极;再进行n型扩散,形成发射极,从而实现紧邻的两个p-n结。

通过图中可以看到,在BJT器件中,电流在垂直方向进行流动,所以集成电路中的BJT器件是垂直器件。

图:BJT器件截面和简化模型

HBT:一种特殊的BJT器件

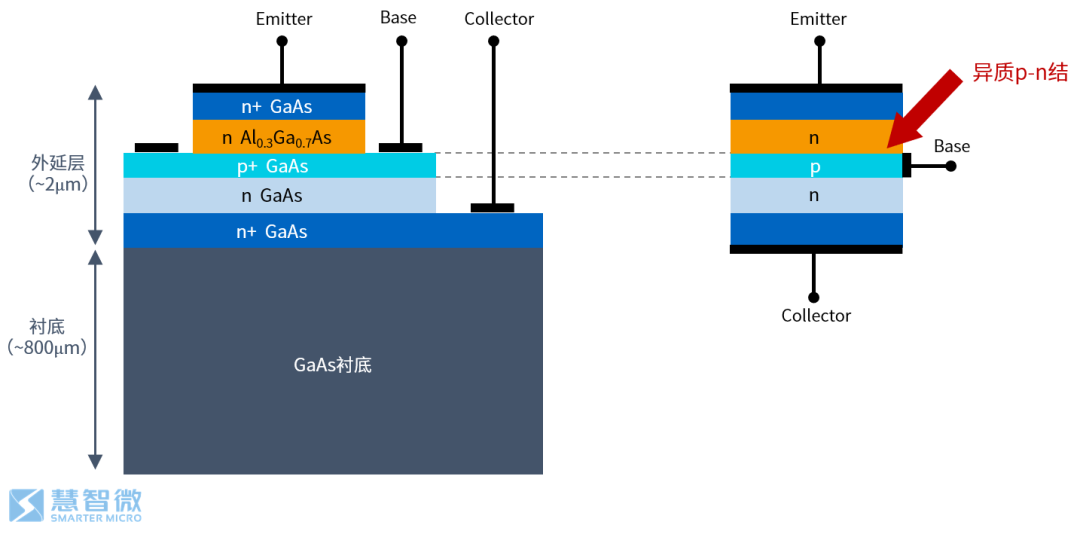

HBT的全称是Hetero Junction Bipolar Transistor,中文名为异质结双极型晶体管。HBT是一种特殊的BJT器件。

HBT对普通BJT的改进是在发射极和基极之间采用不同的半导体材料,形成异质p-n结,来抵挡住基极载流子向发射极的注入,这样就可以使发射极中更多的载流子流入集电区,从而提高集电极到发射极之间的电流。外围观察到的现象是基极的电流变小了,集电极电流变大了,基极电流对集电极电流有了更强的控制能力。

常见的HBT器件有GaAs HBT器件、SiGe HBT器件。下图为典型的GaAs HBT器件横截面图。

图:GaAs HBT器件截面和简化模型

AlGaAs/GaAs是研究最广泛,应用最广泛的异质结系统。5G射频PA中所使用的GaAs HBT,就是此种类型的异质结HBT。在AlGaAs/GaAs异质结HBT中,基极p+ GaAs层与发射极n+ GaAs中间,注入了n型Al0.3Ga0.7As发射区薄膜,从而形成了基极与发射极之间的异质p-n结。

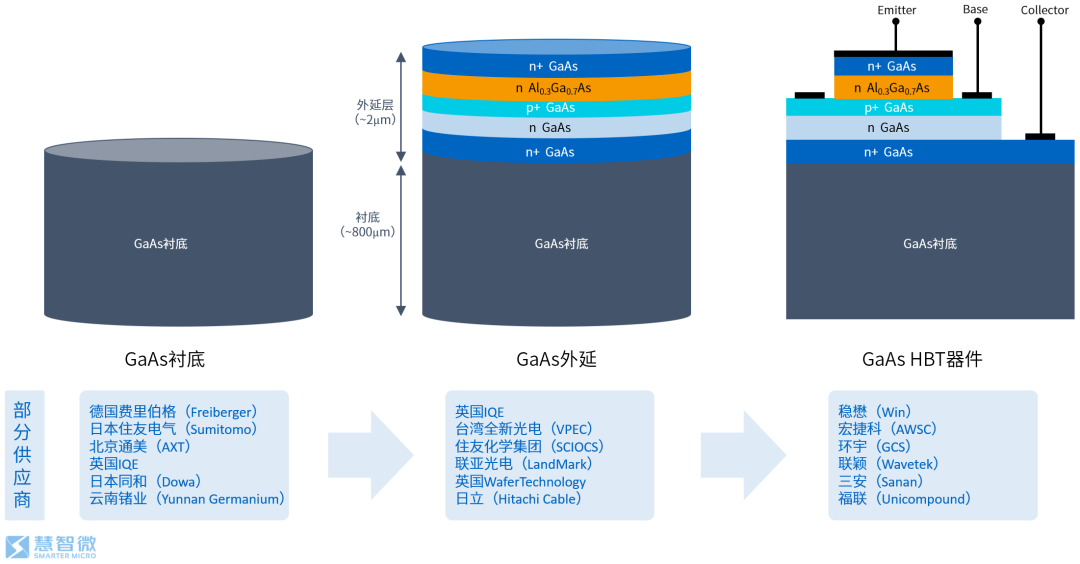

外延层:HBT器件的关键材料

在HBT器件的结构中,可以看到HBT器件截面由外延层、衬底两部分构成。

在集成电路中,晶圆制备包含衬底制备和外延工艺两大环节。衬底(Substrate)是由半导体单晶材料制造的晶圆原片,衬底可以直接进入晶圆制造环节生产半导体器件,也可以进入外延工艺,生长完外延层后,再进行半导体器件制造。

外延(Epitaxy,简称Epi)是指在单晶衬底上生长一层新单晶的过程,由于是在衬底上延伸生长,所以被称为“外延”。外延层一般只有几微米厚,外延出来的新单晶可以和衬底是同一材料,也可以是不同材料。

外延工艺解决了器件只能使用一种衬底材料的问题。使器件不同区域使用不同材料成为可能,极大地增加了器件设计的灵活性。对于HBT器件,由于需要设计AlGaAs/GaAs的异质半导体p-n结,就需要使用外延层工艺将不同材料及掺杂的半导体材料层设计出来。

通过不同外延层的设计,还可以对HBT器件的特性进行调整。HBT器件的性能依赖于器件中发射极、基极以及集电极的厚度及掺杂浓度曲线,这些数据都是在外延层的设计中进行调整。

在HBT生产产业链运行中,一般由衬底厂商生产出GaAs衬底,再交由外延厂商生长外延层,最后交由代工厂生产出HBT器件。由于外延层材料中半导体器件的材料参数已确定,所以外延层的生长是HBT器件生产的关键步骤。

图:GaAs HBT器件产业链流程

FET器件

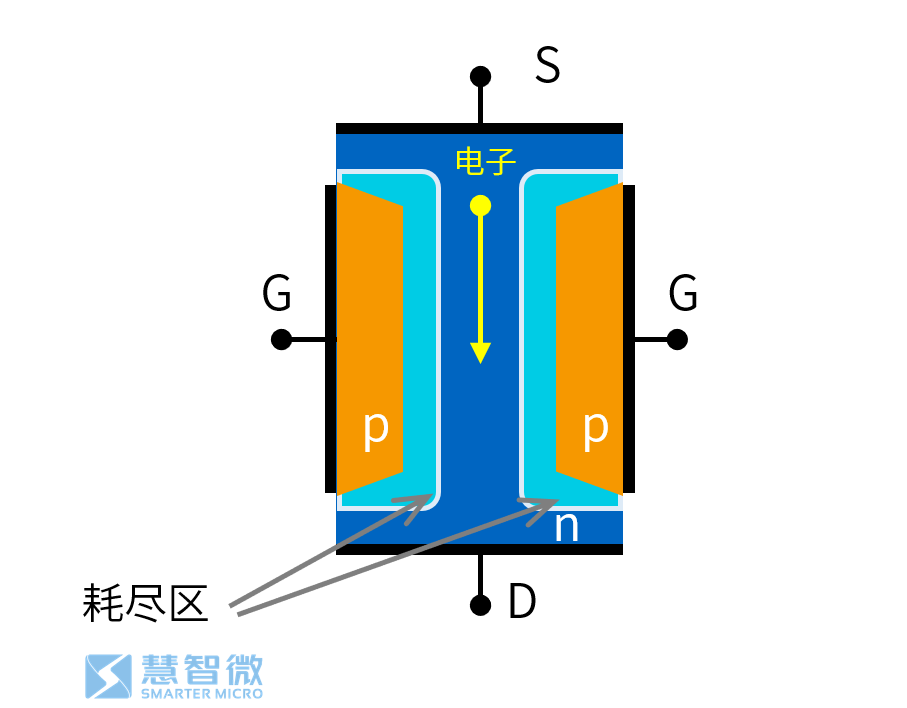

FET器件的全称是Filed Effect Transistor,中文名是场效应晶体管。晶体管名称前面的Filed Effect(场效应)指的是用电场(Electric Filed)来控制半导体内电流流动的器件。

FET的思路非常简单直接,在一个经过掺杂的半导体材料(如n型)两边,加上另一种掺杂的半导体材料(p型),通过控制p型掺杂上的电压,就可以控制n型沟道的夹断或者导通,就达到了控制电流的目的。FET的工作原理,更加像水龙头了。

在FET器件中,由于参与导电的只有一种载流子(如n型沟道FET器件中的电子),这与BJT器件有电子与空穴均参与导电有很大的不同。所以最早的FET器件又叫Unipolar Transistor(单极晶体管),以强调这种单一载流子导电特性。

在n沟道FET器件中,有三个极,分别是提供电子的源极(Source,S极),流出电子的漏极(Drain,D极),以及控制沟道的栅极(Gate,G极)。

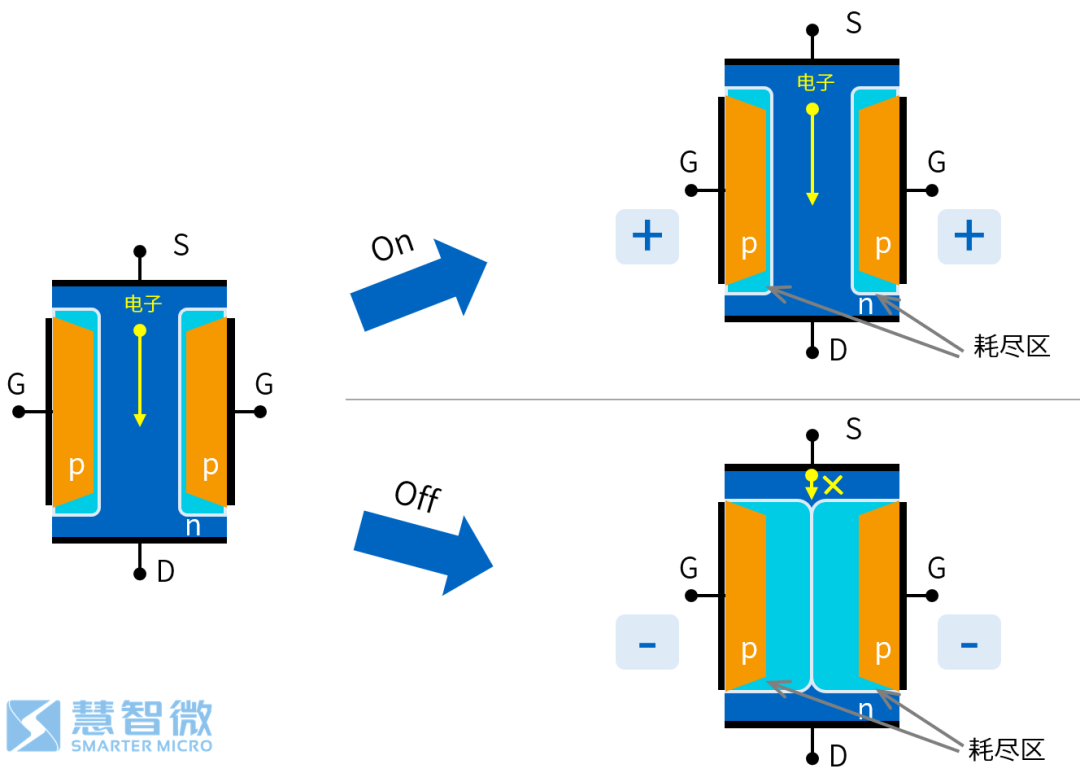

图:FET器件的原理示意

相比于BJT器件复杂的p-n结运行理论,FET器件的概念简单直接,“沟道”和“夹断”,非常符合人们的直觉,所以FET的理念在BJT商用之前就被提出来。

在1926年J. E. Lilenfeld申报的专利文件中,最早提出了FET的理念[1]。比1947年贝尔实验室的肖克利团队发明BJT器件还要早21年。但由于当时工艺所限,FET器件只存在了前期科学家们脑中的概念之中。一直到1953年,得益于工艺进步,FET器件才被真正生产出来。第一个被生产出来的FET器件是JFET(Junction FET)器件。

JFET

JFET是首个被正式生产出来的FET器件。因为名称中有“Junction,结“,所以JFET的工作中也利用到了p-n结特性。

图:JFET的构造及工作原理

JFET由肖克利团队于1952年首次提出并加以分析。在JFET中,所加的栅电压改变了p-n结耗尽层宽度,进而改变了源、漏极之间的电导。

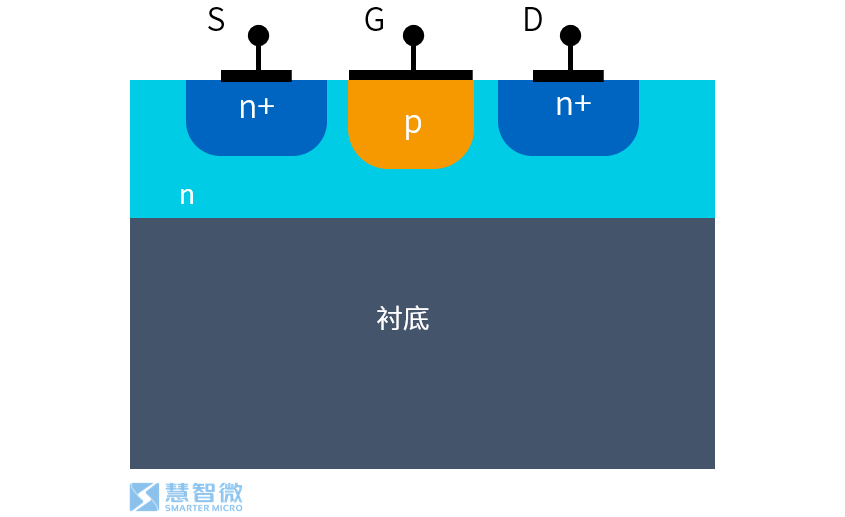

经过多年工艺进步,JFET的结构也有了变化,下图为现代的JFET结构,虽然在物理外观与最早的JFET有些不同,但仍然是利用电场控制栅极p-n结,等效于最早的肖克利结构。

图:现代的外延层JFET器件结构

MESFET

MESFET的是Metal-Semiconductor FET的缩写,中文名是金属-半导体接触场效应晶体管。MESFET是利用金属与半导体接触的特性开发的晶体管。JFET与MESFET的结构比较如下。

图:JFET与MESFET的结构对比

MESFET的工作原理与JFET类似,唯一不同点是用于控制沟道夹断与否的并不再是p-n结,而是金属-半导体结(简称金-半结)。

金属-半导体接触是在半导体理论研究中非常重要的研究,在许多半导体器件中都有广泛的应用。金属-半导体接触最早始于1874年半导体物理理论的建立时期,1938年,Schottky(肖特基)完成了金属-半导体势垒理论,完成了理论体系。于是,形成肖特基势垒的金属-半导体接触又叫肖特基接触,由此开发的二极管叫肖特基二极管。除了肖特基接触外,金属与重掺杂的半导体接触还可以形成欧姆接触,这是所有半导体器件流入和流出所必须的。

商用产品中被广泛使用的MESFET器件是GaAs基MESFET,得益于GaAs的电子输运特性,GaAs MESFET有良好的射频性能,是现在单片微波集成电路(MMIC)的核心。

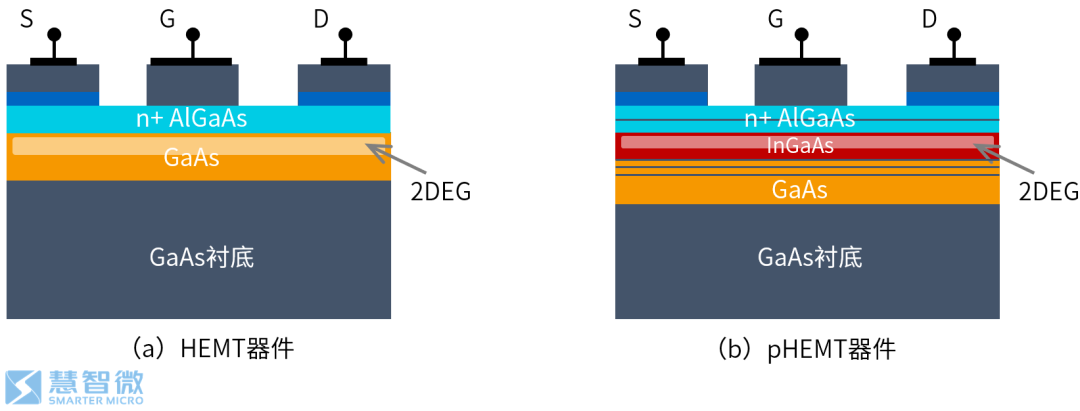

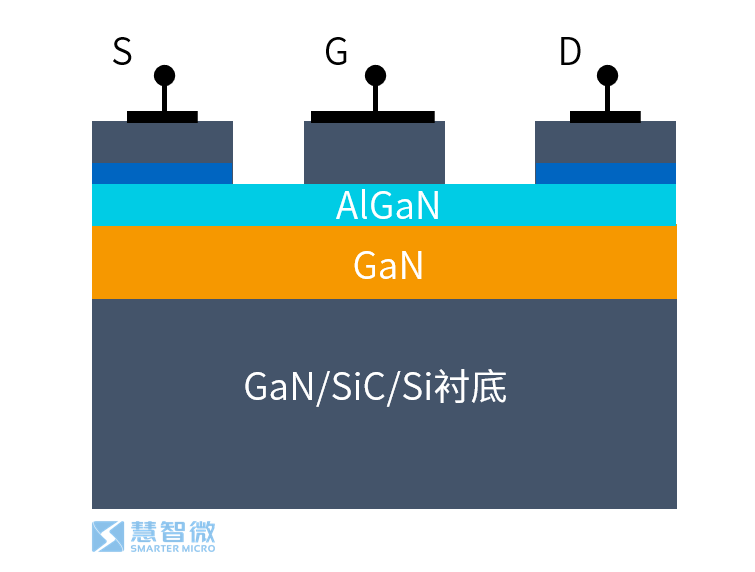

HEMT及pHEMT

HEMT的全称是High Electron Mobility Transistor(高电子迁移率晶体管)。HEMT最早由日本Fujitsu公司于1979年发明。HEMT器件的想法是,利用不同半导体材料异质结的特性,在接合面上聚集大量的电子,形成一种名叫“二维电子气(2DEG)”的高移动层,达到更好的器件性能。HEMT器件在高频毫米波领域、低噪声领域有着不可替代的应用。

因为利用到了异质结,所以HEMT又被称为异质结FET (Heterostructure FET,HFET)。下图为HEMT器件的典型架构。

图:HEMT器件的典型结构

通常情况下,异质结接触表面会存在晶格失配,这个失配会影响到器件性能,也影响到更大带隙电压材料的选取。于是就有了一种改进型的HEMT器件:pHEMT。

pHEMT器件的全称是Pseudomorphic HEMT。Psedomorphic的意思是假的、赝配的,pHEMT器件在异质结转换时加入薄的“赝晶层”,用于将两边的晶格拉向匹配。

图:HEMT与pHEMT器件结构示意图

由于出色的射频性能,pHEMT器件在高性能射频微波领域应用广泛。尤其是GaAs pHEMT器件,是微波低噪声放大器、微波毫米波电路的重要半导体工艺。

与HBT器件相同,HEMT及pHEMT器件的特性强烈依赖于材料特性,在HEMT/pHEMT产业链中,同样需要外延层厂商生产出相应的材料外延,再由代工厂进行器件加工。

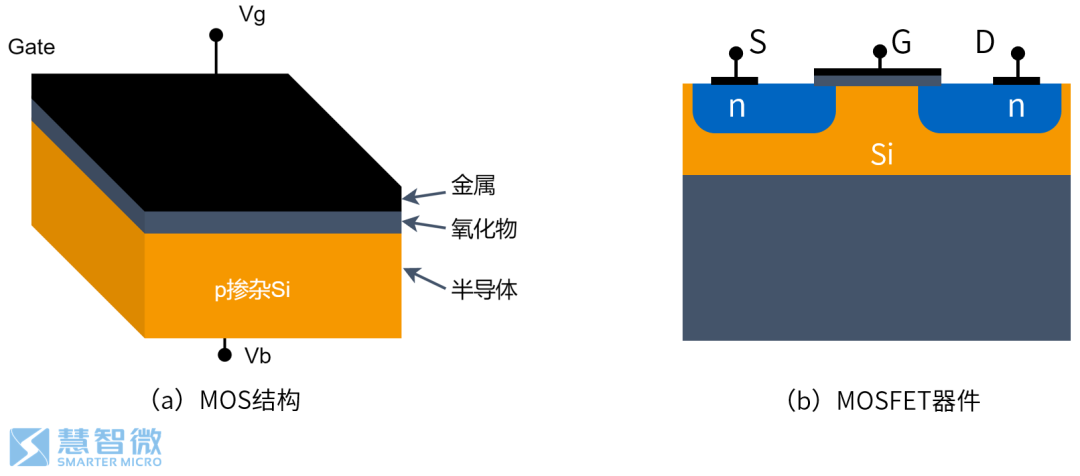

MOSFET

MOSFET结构毫无疑问是当今集成电路领域最为核心的结构。

MOSFET缩写自Metal-Oxide-Semiconductor FET(金属-氧化物-半导体 FET),MOSFET是MIS(Metal-Insulator-Semiconductor,金属-绝缘层-半导体)器件的一种特殊结构。下图为典型MOS结构,以及MOSFET的示意图。

图:MOS结构及MOSFET器件结构

在MOSFET之前,已经有了平面结构的MESFET器件与垂直结构的BJT器件,但这两种电路都无法适应于大规模电路的设计:

垂直结构的BJT器件无法做到有效集成;BJT器件的工作机理使得器件无法有效关断或打开;Base端的电流也使BJT器件有较大的工作电流

MESFET虽然是平面器件,解决了集成的问题,但MESFET器件所使用的金属-半导体结会钳位住过大Gate电压, 造成Vg只能在一定范围内使用

于是,MOSFET器件被发明了出来。

现代MOSFET器件的提出在1960年,Ligenza等人提出了基于Si-SiO2结构的MOSFET器件,改变了MESFET的一系列缺点,适合大规模集成,适合尺寸等比例缩小。自此,半导体器件再也不是一个个单独的晶体管,大规模集成电路的序幕就此拉开。

基于MOSFET器件的半导体结构多种多样,主要有CMOS、SOI、Fin-FET等。

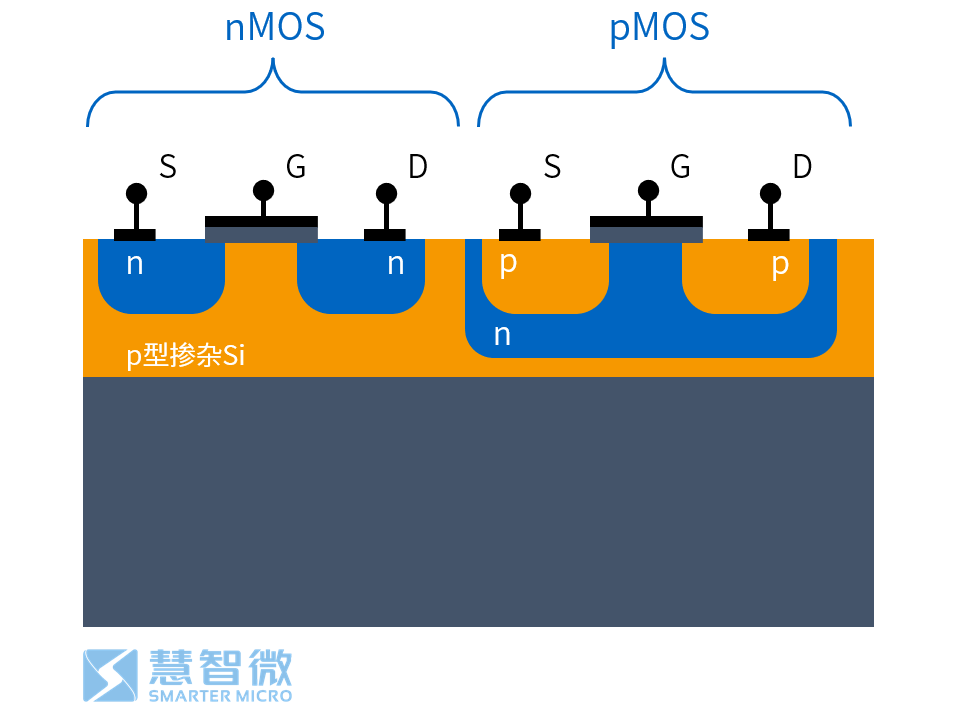

CMOS

CMOS电路的发明,使集成电路进入到了“等比缩小”的快车道,是人类集成电路史上的一大飞跃。

CMOS的全称是Complementary metal–oxide–semiconductor(互补型MOS),“互补”的意思是电路中不止由nMOS,还有pMOS。两种MOS器件结合进行设计,就可以完美完成数字集成电路中的逻辑电路设计。

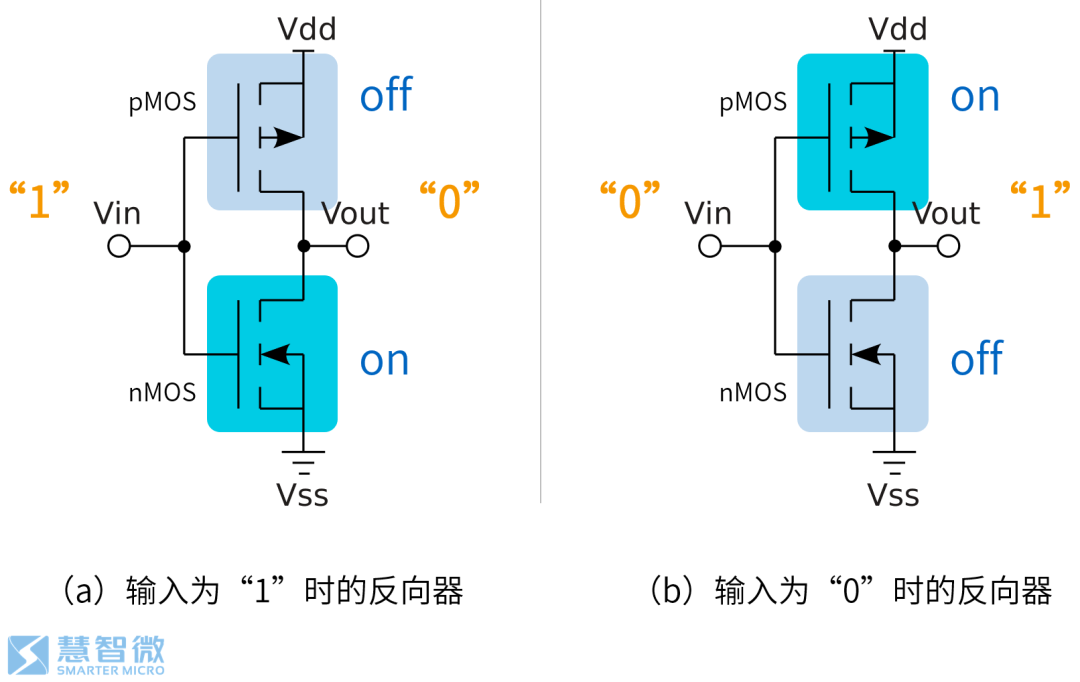

虽然也可以用BJT器件设计类似TTL(Transistor-Transistor Logic),但CMOS逻辑的优点在于静态功耗低。如下图简单反向器为例,在同一时刻,通路中的nMOS与pMOS只有一个器件导通,理论电路静态功耗为0。

图:CMOS反向器工作原理说明

图:CMOS器件的基本结构

CMOS器件被发明之后,人们发现这项技术与数字电路技术相得益彰、珠联璧合。数字电路需要的是小尺寸、低功耗的基本逻辑单元,而CMOS器件刚好可以满足这个需求。于是,人类不断改进半导体工艺,使CMOS器件尺寸不断缩小,以使数字电路的能力越来越强大。

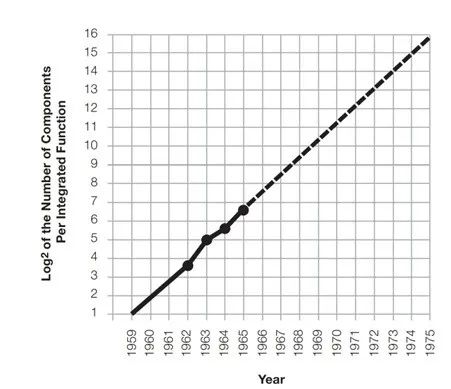

1965年,仙童公司的Gordon Moore(戈登·摩尔)在Electronic Magazine杂志中发表了一篇简短的文章,预测1965年到1975年期间:集成电路上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍。换言之,处理器的性能大约每两年翻一倍,同时价格下降为之前的一半[4]。

图:戈登·摩尔在1965年提出的“摩尔定律“

不过,让戈登·摩尔没想到的是,摩尔定律有效性绝不是在他预期的1965-1975年的10年之内,而是支撑整个集成电路行业发展了近60年。在这60年里,处理器上的晶体管数目从几百个增加到了几十亿甚至几百亿个,CMOS器件特征尺寸由几毫米缩小到了几纳米。在高通发布的8系列智能手机平台芯片里,采用4nm工艺,集成了近200亿个晶体管。小小的集成电路,有了无与伦比的强大功能。

图:高通骁龙8系列手机平台芯片,采用TSMC 4nm工艺设计

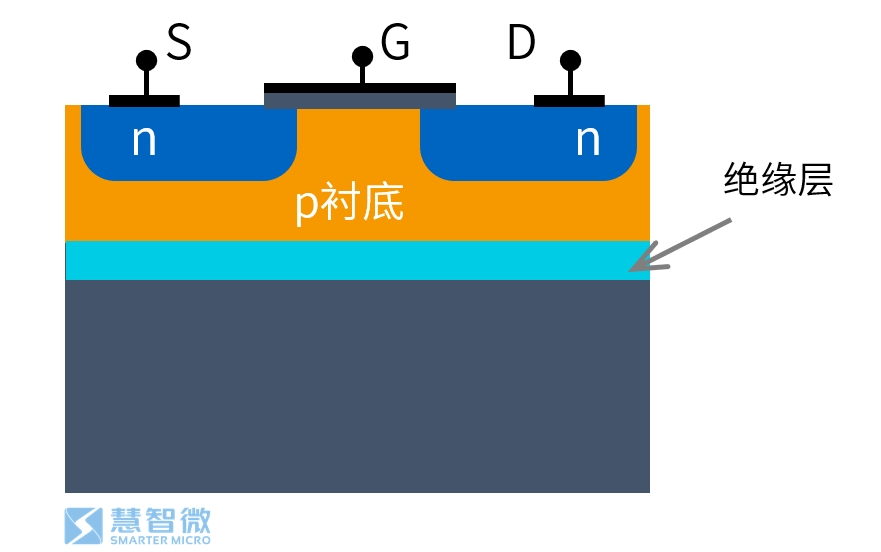

SOI

SOI的全称是Silicon on Insulator,绝缘体上硅。是指在带有绝缘层的硅衬底上生产半导体器件的技术。SOI技术可以减小衬底损耗对器件的影响,因此有较好的器件特性。SOI技术生产的半导体器件如下图所示。

图:SOI器件基本结构

Fin-FET

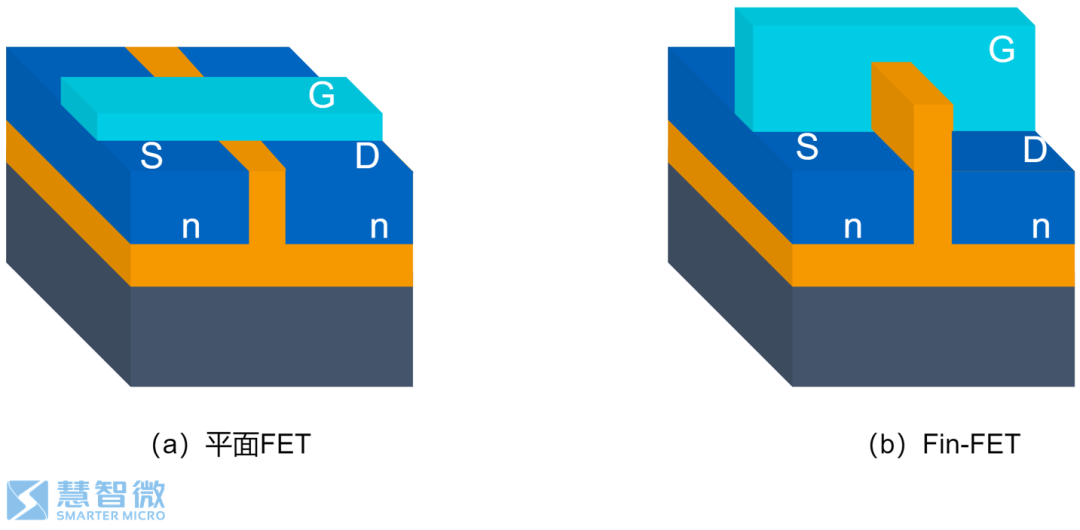

Fin-FET中文名称是鳍式场效应晶体管,根据其形状像鱼鳍来命名。是在摩尔定律的推动下,为使器件尺寸不断减小,所发明的一种器件结构。

在Fin-FET发明之前,随着摩尔定律使器件尺寸不断减小,原来平面结构的栅极已经没办法控制住器件的沟道,器件漏电流明显。于是,加州大学伯克利分校的胡正明教授于1999年提出Fin-FET结构,这种结构将栅极由平面结构升级成鱼鳍状的三维结构,于是形成了更好的对沟道的控制。

图:从平面CMOS FET,至Fin-FET

目前,TSMC、Intel、三星等均采用Fin-FET进行先进CMOS工艺的设计。

以材料分类半导体

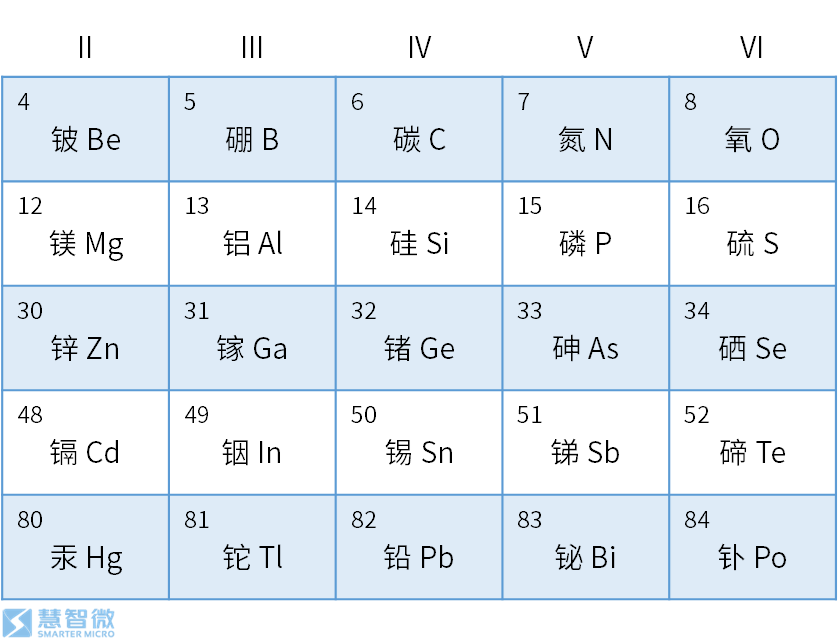

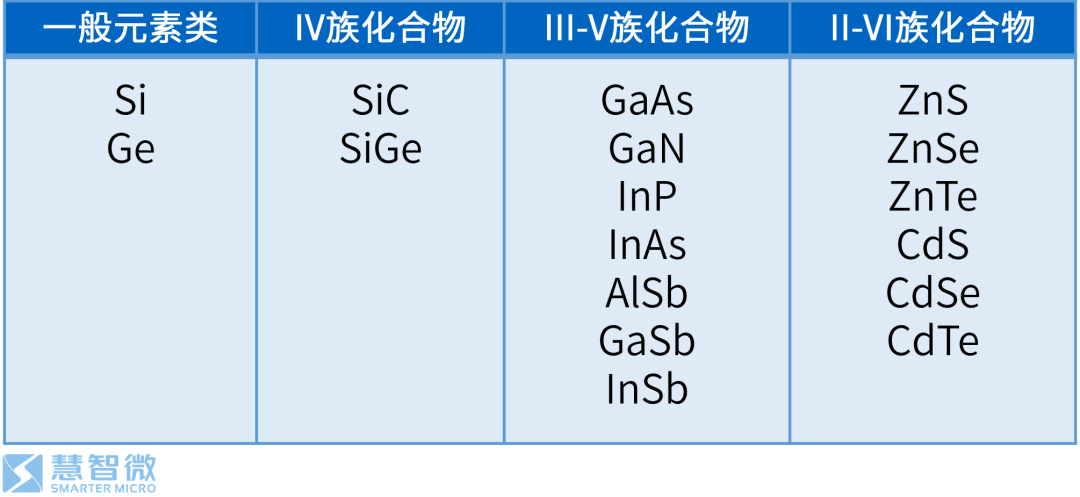

除了根据器件的不同分类,半导体还可以根据材料的不同来分类。

半导体材料种类非常多,用于制作半导体的材料不仅有我们熟悉的硅材料,还有锗。另外,一些化合物材料如GaAs、GaN、SiC等,也都是常见的半导体材料。下表列出了在元素周期表中处于II-VI族的部分元素,这些元素或者这些元素的集合可以构成典型的半导体材料。

图:用于半导体的常见材料元素

需要说明的是,用于半导体的材料很多,甚至在一个半导体器件中,就会有不同的半导体材料。在对一个器件命名时,一般以构成该半导体器件重要部分(如沟道)的材料对其命名。

比如对于下图GaN HEMT器件,虽然器件可以生长在Si或者SiC衬底上,但是器件的沟道是由GaN,以及GaN和AlGaN的异质结构成,所以器件称为GaN HEMT器件,或者AlGaN/GaN HEMT器件。

图:GaN/SiC/Si基GaN HEMT器件示意图

材料与结构的结合

如文章开头所述,材料与器件结构结合,才可以对器件进行准确描述。完整的器件名称应为“材料+器件结构”。

理论上,不同材料和器件结构之间可以任意两两结合。不过,由于材料特性和特殊需求的关系,并不是所有材料上都可以生长出任意类型的器件。在使用中,主要的材料与结构结合器件如下。

图:不同材料和结构的半导体器件

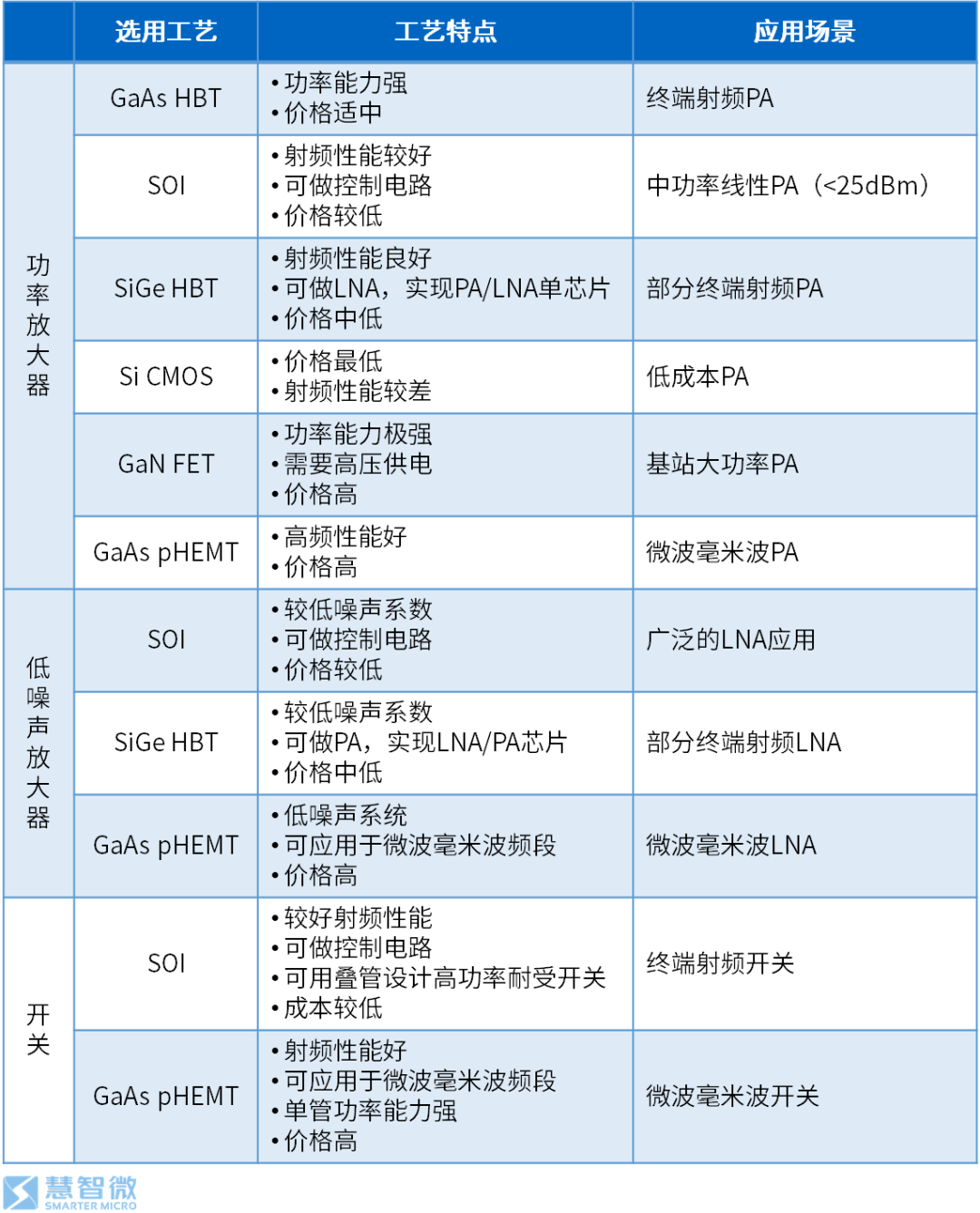

5G射频中的半导体器件

在射频前端芯片设计中,也需要用到多种半导体工艺。射频前端各模块常用的半导体工艺及工艺特点总结如下:

总结

66年前,世界上第一个半导体晶体管在贝尔实验室诞生,此后,随着半导体工艺发展、集成电路的发明,小小的半导体器件改造了人类生活的方方面面。

射频技术也深受半导体技术的影响。无论是手机终端中所使用的模组芯片,还是基站中所使用的半导体单管,半导体器件作为核心元器件,成为当今射频技术的基础。

不过半导体技术抽象、半导体器件纷杂,很多时候没有办法直接和日常使用结合起来,这给大家平时的工作造成非常多的困扰。

本文将射频各模块中常见到的半导体器件类型做了整理,希望可以在需要的时候给大家工作带来帮助。

本文整理过程中,得到众多专家的指导,在此表示感谢!欢迎大家留言,一起讨论“射频芯片中的半导体”。