(文/李映) 静水深流式的代工市场最近格外不平静。在三星豪言2027年将量产1.4nm、台积电或将重返半导体王座之后,英特尔也抛出了“系统级代工”来强力助攻IDM2.0。

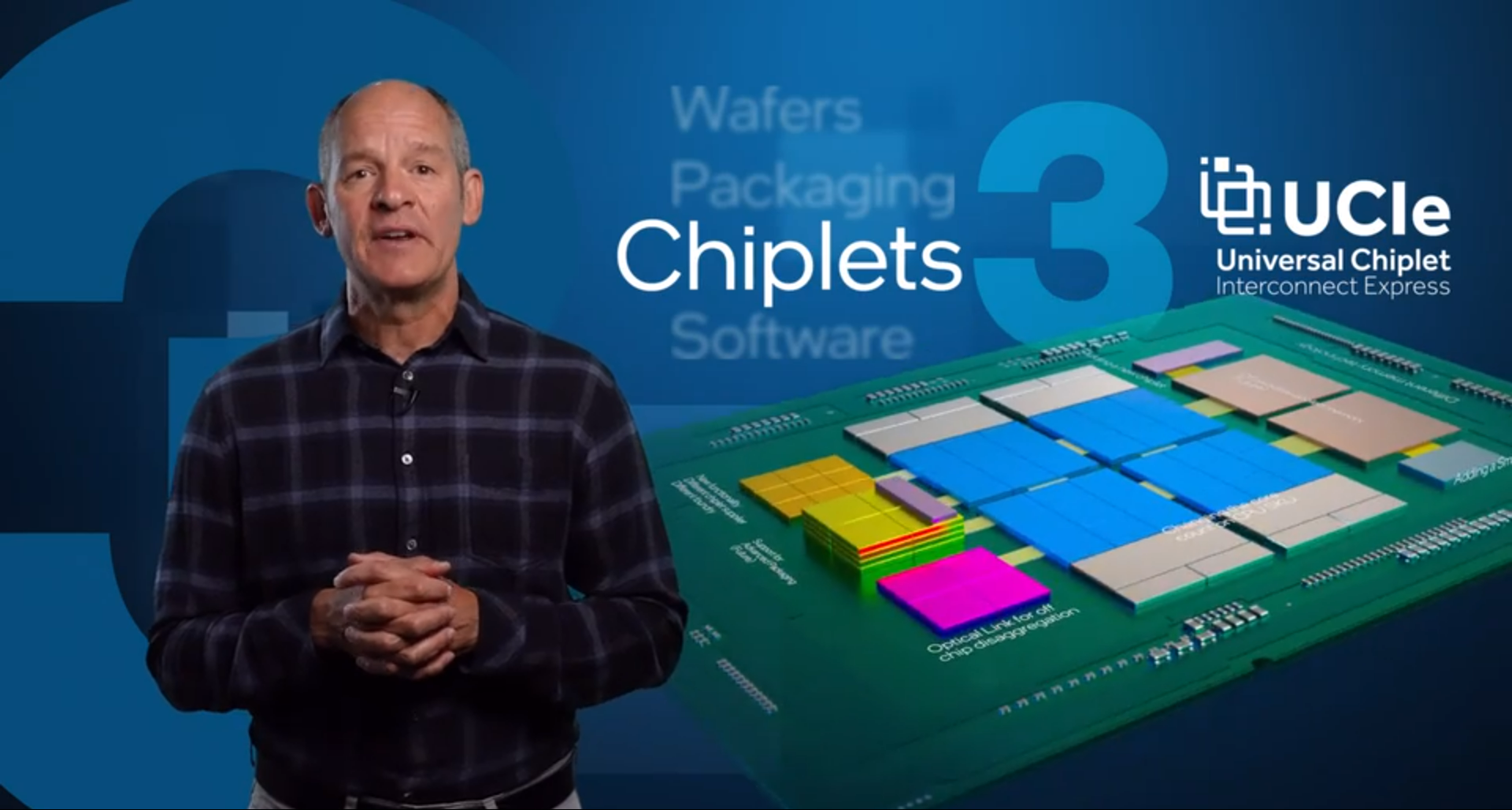

在前不久举行的英特尔On技术创新峰会上,CEO帕特·基辛格宣称,英特尔代工服务(IFS)将开创“系统级代工”的时代,不同于仅向客户提供晶圆制造能力的传统代工模式,英特尔将提供涵盖晶圆、封装、软件和Chiplet(芯粒)的全面方案。基辛格着重表示,“这标志着从系统级芯片(system-on-a-chip)到系统级封装(system in a package)的范式转移。”

在英特尔这一巨轮加速向IDM2.0挺进之后,近来动作不断:无论是开放x86,加盟RISC-V阵营,还是收购高塔、扩充UCIe联盟、宣布数百亿美元的代工产线扩建计划等等不一而足,显现出要在代工市场三分天下有其一的野望。

而今,再祭出系统级代工“大招”的英特尔会如愿在“三皇”会战中增加更多筹码吗?

大势使然

系统级代工概念的“问世”,其实早已有迹可寻。

在摩尔定律放缓之后,实现晶体管密度、功耗、尺寸之间的平衡面临更多的挑战,而新兴应用对高性能大算力以及异构集成的芯片需求有增无减,驱动着业界探寻新的解决之道。

借助于设计、制造、先进封装以及近年来兴起的Chiplet等,来实现摩尔定律的“续命”以及芯片性能的持续跃迁,看起来已成共识。特别是在未来制程微缩受限的情况下,Chiplet与先进封装搭配将会是突破摩尔定律的解法。

而代工厂来充当联接设计、制造和先进封装的“主力”,显然有着先天的优势和能够盘活的资源。意识到这一大势,不论是台积电、三星还是英特尔等这些顶级玩家均在着力布局。

在一位半导体代工行业资深人士看来,系统级代工是未来代工的必然趋势,相当于泛IDM模式的扩展,类似于CIDM,但差异在于CIDM是不同公司通过一个共同的任务来衔接,而泛IDM则是将不同任务整合为客户提供一个Turnkey Solution。

英特尔方面在接受集微网采访时表示,从系统级代工的四大支撑体系来看,英特尔均具备优势技术的积淀。

在晶圆制造层面,英特尔开发了如RibbonFET晶体管架构和PowerVia供电等创新技术,并在稳步实现在四年内推进五个制程节点的计划。英特尔还可提供EMIB和Foveros等先进封装技术,以助力芯片设计企业整合不同的计算引擎和制程技术。而芯粒模块化的部件为设计提供了更大的灵活性,驱动整个行业在价格、性能和功耗方面进行创新。英特尔致力于构建UCIe联盟助力来自不同供应商或不同制程的芯粒更好地协同工作。在软件方面,英特尔的开源软件工具OpenVINO和oneAPI可加速产品的交付,并使客户能够在生产前测试解决方案。

凭借系统级代工的四大“护法”,英特尔展望,单颗芯片上集成的晶体管将从目前的1000亿个大幅扩展至万亿级别,基本可成定局。

“可以看到英特尔的系统级代工目标契合IDM2.0的战略,且有相当的势能,将为英特尔未来的发展打下基石。”上述人士进一步表示对于英特尔的看好。

联想到以“一站式芯片方案”扬名立万的联发科,再到如今“一站式制造”的系统级代工新范式,代工市场或将迎来新的巨变。

胜算筹码

祭出了系统级代工这一大招儿,英特尔其实已然做了诸多铺垫。除却上文提及的各种创新加成之外,还要看到为了系统级封装新范式所付出的诸多努力和整合力道。

半导体行业人士陈启分析,从现有资源储备来看,英特尔拥有完整的x86架构的IP,这是它的底蕴,同时英特尔有PCIe、UCle等高速SerDes类接口IP,可利用这一技术更好地和英特尔核心CPU做Chiplet的组合和直连。而且,英特尔又掌控了PCIe技术联盟标准的制定,而PCIe基础上发展起来的CXL联盟和UCle标准也是由英特尔主导,相当于英特尔既掌握了核心IP,又掌握了非常关键的高速SerDes技术和标准。

“英特尔的混合封装技术、先进工艺能力并不弱,如果能和它的x86 IP内核以及UCIe相结合,确实能在系统级代工时代拥有较多的资源和话语权,并打造出一个全新的英特尔,持续保持强大。”陈启告诉集微网。

要知道,这都是英特尔的看家本领,之前是不会轻易示人的。

“由于过去在CPU领域的强势,系统内关键资源——内存资源被英特尔牢牢把控,系统内其他芯片想要使用内存资源,必须通过CPU获得,因此英特尔可通过此举限制其他公司的芯片,过去业界对这一‘间接’的垄断行为怨声载道。”陈启解读说,“但随着时代的发展,英特尔感受到四面八方的竞争压力,因而主动求变,将PCIe技术开放出来,相继成立CXL联盟和UCle联盟,相当于主动把蛋糕放在了桌子上。”

行业看来,英特尔在IC设计、先进封装领域的技术跟布局仍然十分扎实。以赛亚调研(Isaiah Research)认为,英特尔走向系统级代工模式,是希望整合这两大方面的优势与资源,通过从设计到封装一条龙的概念,差异化其他晶圆代工厂,以在未来代工市场获得更多订单。

“以这样Turnkey solution的方式,对于小型初级开发而且研发资源不足的公司是相当有吸引力的。”以赛亚调研还看好英特尔此举对中小客户的吸引力。

对于大客户,有行业专家直言,英特尔系统级代工最现实的利好还在于可拓展与部分数据中心客户如谷歌、亚马逊等的双赢合作。

“一是英特尔可授权他们在自己的HPC芯片中使用英特尔X86架构的CPU IP,有利于保持英特尔CPU领域的市场份额。二是英特尔可提供UCle之类的高速接口协议IP,更加方便客户将其他功能IP整合。三是英特尔提供完整平台来解决流片、封装的问题,形成最终英特尔深入参与的亚马逊版本Chiplet方案芯片。这对英特尔来说应是一个较完美的商业方案。”上述专家进一步补充。

仍需补课

但做代工需要提供一揽子平台开发工具,以及树立“客户至上”的服务理念,从英特尔以往历史来看,也曾尝试过代工,但结果也不尽人意。借助系统级代工尽管能助力其实现IDM2.0的宏愿,但隐形的挑战依然要着力攻克。

“正如罗马不是一日建成的,代工和封装不是说技术强大就万事大吉的事情,从IDM转型代工,对于英特尔来说,最大挑战仍是代工文化。”陈启告诉集微网。

陈启进一步指出,如果说制造、软件等生态英特尔还可通过砸钱、技术转让或是开放平台模式来搞定的话,英特尔最大的挑战是要从体系上构建代工文化,要学会与客户沟通,为客户提供所需的服务,满足客户差异化的代工需求。

对此以赛亚调研则认为,因为英特尔唯一需要补足的是晶圆代工这部分的能力,相比台积电有持续且稳定的主要客户与产品协助提升每段制程良率,英特尔多半只生产自家产品,在产品类别与产能有限的情况下,英特尔芯片制造的优化能力有限。通过系统级代工模式,英特尔有机会通过设计、先进封装、芯粒等技术吸引部分客户,从少量多元的产品一步步提升晶圆制造的能力。

此外,先进封装和Chiplet作为系统级代工的“流量密码”,也面临各自的难关。

以系统级封装为例,从其涵义来看,相当于晶圆产出之后要实现不同Die之间的整合,但这殊非易事。以台积电为例,从最早为苹果做方案到后来为AMD做代工,台积电在先进封装技术方面花费多年时间,并推出了多个平台,如CoWoS、SoIC等,但到最后多数依然是一对一定制化封装服务,并不是传言中为客户提供“芯片像搭积木一样”高效的封装方案。

最终,台积电将各种封装技术整合后推出3D Fabric代工平台,同时抓住机会参与了UCle联盟的组建,想方设法将自己的标准和UCIe标准打通,有望后续“搭积木”的推进。

芯粒结合的关键在于统一“语言”,即标准化Chiplet接口。为此英特尔也再次挥舞起影响力大旗,以PCIe标准为基础着力为芯片到芯片互连建立起UCIe标准。

显然这还需要时间让标准“通关”。The Linley Group总裁兼首席分析师Linley Gwennap在接受集微网采访时就提出,业界真正需要的是将芯粒连接在一起的标准方式,但各公司需要时间来设计新的芯粒以满足新兴标准。目前虽已取得了一些进展,但仍需要2-3年的时间。

一位半导体资深人士从多维角度表达了疑虑,英特尔在2019年退出代工服务不到三年重返,试图从IDM转型打造新的服务模式,能否再被市场接受,需时间观察。从技术来看,英特尔2023年预计推出的下一代CPU在制程和存储容量、I/O功能等方面仍较难展现优势。此外,以往英特尔的制程蓝图有过几次推迟的记录,而现在同时要进行组织重组、技术提升、市场竞争、建厂等多项艰难任务,相较过去的技术挑战,似乎更增添了未知的风险。特别是英特尔能否在短期内建立起新型系统级代工模式的供应链,亦是一大考验。(校对/王丽英)