“随着数字经济的发展,算力已日趋重要,据测算算力指数每提高1个百分点数字经济和GDP将分别增长3.3%和1.8%。”中国联通研究院副院长、首席科学家唐雄燕在近日举办的第二届SmartNIC&DPU技术创新峰会上指出,“而算力的发展和网络的演进都是相辅相成的,算力网络的作用在于如何找到合适的算力节点,网络则发挥打通数据到计算节点的通路作用。”

左手算力、右手网络的算网时代正加速驶来,也开辟出最后一米的DPU“新阵地”。

对此唐雄燕分析,传统计算架构是将数据送到计算节点之后由CPU来处理,但随着网络体系从以计算为中心转向以数据为中心,CPU无法避免地面临虚拟化层、流量处理和异构算力开销导致的性能损失,因而以CPU为中心的计算架构亟须变革。由智能网卡进阶而生的DPU从过去简单的协助CPU进行网络报文的处理到实现虚拟化的全卸载和任务全生命周期管理,承担执行网络、存储、安全等任务的同时形成天然、安全的隔离层的重任,将解决从数据到计算“最后一米”的问题,晋身为CPU、GPU之后的第三大算力芯片。

但真要解决“最后一米”,殊非易事。从全局来看,DPU的设计、生态和应用还处于探索期,还要经过架构迭代、标准规范、商业模式的淬炼,才能为未来的大规模商用铺好道路。

算力网络DPU助攻

算力网络的概念可谓应运而生。

从算力与网络的演进来看,从90年代初到2010年,实现了计算机联网之后出现了互联网,算力为分布式的算力;从2010年到2020年,最重要的发展是云计算,云计算实现了多服务链接,适应云计算的网络也随之变革,出现了云化网络,SDN/NFV得以快速发展;从2021年之后,随着5G、人工智能以及边缘计算的进一步发展,进入到了万物互联时代,算力网络浮出水面。

唐雄燕从运营商的角度谈及,算力网络可看作是网络云化发展的下一个阶段以及为社会提供智能基础设施(Network for AI)的体系,总体是为了提高“端、边、云”三级计算之间的协同效率。国内的运营商也在希望通过构建计算与网络深度融合的基础设施,着力实现计算跟网络融合的服务。

而DPU在算网时代的潜在价值也将得到“印证”。唐雄燕解释说,DPU在NFV业务层可提升处理万兆流表、报文处理等能力,且现有NFV的业务层、虚拟化层和硬件层的解耦推进缓慢,通过探索将虚拟化层下沉到DPU的方案可更助力推动三层解耦,推进通信云NFV的架构更开放。同时,对于5G来说UPF用户面十分关键,而UPF的一些功能实际上也可通过DPU卸载,以降低处理时延、抖动、丢包率,提高UPF的转化效率的同时还可降低建设成本。此外,在涉及5G行业专网的低时延抖动场景、低成本极边缘UPF一体机、边缘计算场景等层面,DPU仍可发挥重要作用。

对此云脉芯联创始人&CEO刘永锋也表达了类似的观点,他提到,随着数据中心规模逐渐扩大和承载业务的多样化,技术架构演进变化最多的是网络,底层网络技术经历了比较明显的代次演进,从IT机房阶段的二层网络、IT数据中心阶段的三层网络到云原生数据中心阶段的虚拟网络,分别对应于计算联网、计算云网和智算云网。

网络的代次演进也让CPU为更多的基础设施服务消耗着越来越多的算力,在CPU算力增长遭遇瓶颈、业务数据和网络带宽不断增长的情况下,为进一步解决高性能、低延迟的问题,DPU成为新的助攻手。

“这也表明DPU的出现和网络架构本身的演进有紧密联系,要站在网络的入口解决这个问题,其不仅仅是为解决CPU的算力瓶颈,而是要通过先天的网络属性,在数据中心整体TCO的维度提升算力。”刘永锋对此强调。

在芯片已成为美国打压竞争对手的战略工具之际,无疑DPU也相应承载着更高的使命。芯启源DPU事业部总经理侯东辉提到,我国正大力推进数字新基建以及“东数西算”巨大工程的落地,DPU应保证大算力的前提下实现低功耗。同时,算力网络需将业务下沉,分布式存储、边缘计算、超算都成为必须,新场景下信息安全问题也至关重要。此外,DPU作为一个全新赛道,既要保证供应链的安全性自主可控,亦需迎头赶上。

面临设计、成本、生态等挑战

尽管一面世就“贵”为第三代算力芯片,但责任重大的DPU面临的挑战亦不可小觑。在集微网与多位行业人士的交流中得知,DPU仍面临设计、成本、生态等诸多挑战。

从设计来看,中科驭数联合创始人兼CTO卢文岩谈到,DPU与CPU、GPU等功能上的区别在于其是典型的三层功能平面,即数据平面、控制平面及管理平面,而这三个平面对于并行度、性能、灵活性、可靠性的要求差异巨大,比如说数据平面可能对性能和平行度要求非常高,但对于灵活性和可靠性要求不太高。而控制平面对于并行度要求没那么高,但对性能有一定要求并且还要与数据面频繁交互等。

“很显然,三种不同的功能在一起对DPU的设计带来了巨大的挑战。”卢文岩总结说。

作为英伟达资深DPU解决方案架构师,陈志辉则从数据中心场景具象需求出发探讨其挑战。陈志辉认为,DPU可支持多种不同的应用场景,但目前最核心的应用场景还是卸载和加速数据中心的基础设施服务,以大幅提高数据中心服务器的利用率,产生较高的投资收益比。

“而数据中心基本上可看成是一个软件定义的,其核心的基础设施服务都是基于软件来实现并部署在商用服务器上,因而用DPU来运行和加速基础设施服务就必须支持软件定义这一属性。总体来看,DPU的挑战在于:因功耗的限制,DPU通用算力不能无限扩充,需借助加速器来支持100G或200G高性能网络数据面的处理。而且,不同的云厂商基础设施服务的实现和要求不一,需具备快速迭代开发和灵活部署的能力,DPU的设计必须平衡性能和可编程性的需求,以有效应对DPU在云数据中心面临的挑战。”陈志辉详解道。

饶是过了设计关,部署时的成本、标准、生态等考验也还要着力“通关”。

对此唐雄燕提到,一是DPU在场景部署中需成本和场景的平衡,即根据具体的业务和场景选择DPU、CPU的分工与协作使得效益最大化。二是体系重构。前期NFV标准是以CPU为中心的计算体系来构建的,转到以DPU为中心的数据体系将带来NFV虚拟化和通信云的重构,需行业研究相应的体系。三是标准化,现阶段各大厂家的硬件加速方案不尽相同,需要行业制定统一技术标准。四是集成和运维,运营商对DPU的集成与运维支撑体系尚未建立和完善。

此外,生态也是不容忽视的问题。卢文岩表示,DPU 厂商均遇到生态的问题,特别是跨平台方面面临适配困境。“比如CPU有基于x86或Arm的,还有多种操作系统如CentOS、麒麟等。举例来看,公司的DPU和x86和CentOS适配可达到高性能,网络延时可达1.2微秒,达到业界领先,但当DPU和Arm架构CPU适配时延时却增至1.6微秒,再把操作系统换成麒麟时发现跑不起来了,这是巨大的挑战,也需做大量的工作来优化。

破解上述挑战,刘永锋认为DPU的融合、开放、极致是关键。DPU需一个全新的融合架构来实现进一步的软硬件融合,可支持云原生的软件定义接口。在开放层面,需具备灵活的可编程能力,同时向上兼容面向应用的开放软件接口。极致则是指DPU最终需要通过创新架构实现极致的高带宽、低延迟,极致的高性能、低功耗和极致的大规模、高可靠。

迈普通信技术总监郑展伟则认为,要着力实现DPU技术、产品和生态的领先性,而生态领先性就要以开放的操作系统以及开放的智能网卡框架为依托,加上与之匹配的应用以及上下游环节的支持,才是达成生态领先性唯一的途径,并走向真正的繁荣。

不同路线的张力

尽管给DPU下定义的关键词在于:是以数据为中心构造的专用处理器,采用软件定义的技术路线去支撑基础设施层如虚拟化、存储、安全等一系列功能。但无疑开发DPU是一项长周期、高投入、高难度的持久战,国内初创企业创始人有各自不同的技术背景和经验,对于DPU架构和发展路径,却是神仙打架各有主张。

从架构层面考量,卢文岩从已有芯片的两大维度即负载特征和芯片架构出发举例说,如以控制为中心、计算密集型的芯片最典型的是CPU;以控制为中心、I/O密集的是更传统的交换机网络处理芯片;以数据为中心、计算密集性型的芯片如GPU、AI等;而以数据为中心、I/O密集型的则是DPU。因此DPU可说是第四类的算力芯片,在结构上和CPU、GPU一定是不一样的,它应该是一个异构多核的架构,不同的核要去处理不同的任务,但也要有足够的灵活性,尤其在数据平面能去面向一些领域专用的语言,提供软件和编程的能力。

在具象的呈现上,侯东辉判断,DPU是一款可编程的、软件定义的SoC芯片,可根据不同的客户需求和不同的场景做相应的定义开发,同时要构建一个开放的生态。尽管运营商之前的NFV是基于CPU的架构,但DPU本身是一个支持网络通信协议和指令级的专用芯片,可助力运营商更好地实现NFV网络的虚拟化和提速业务场景。

但星云智联解决方案部长马国强对此表达了相左的看法,马国强从场景、资源利用率、运维效率出发总结说,DPU应是一个多技术路线、多形态的解决方案,而不是经常讨论的SoC芯片。通过对数据面、控制面、管理面等来考量,它的形态可以是CPU+FPGA、CPU+ASIC或者是将CPU和ASIC整合于一体。

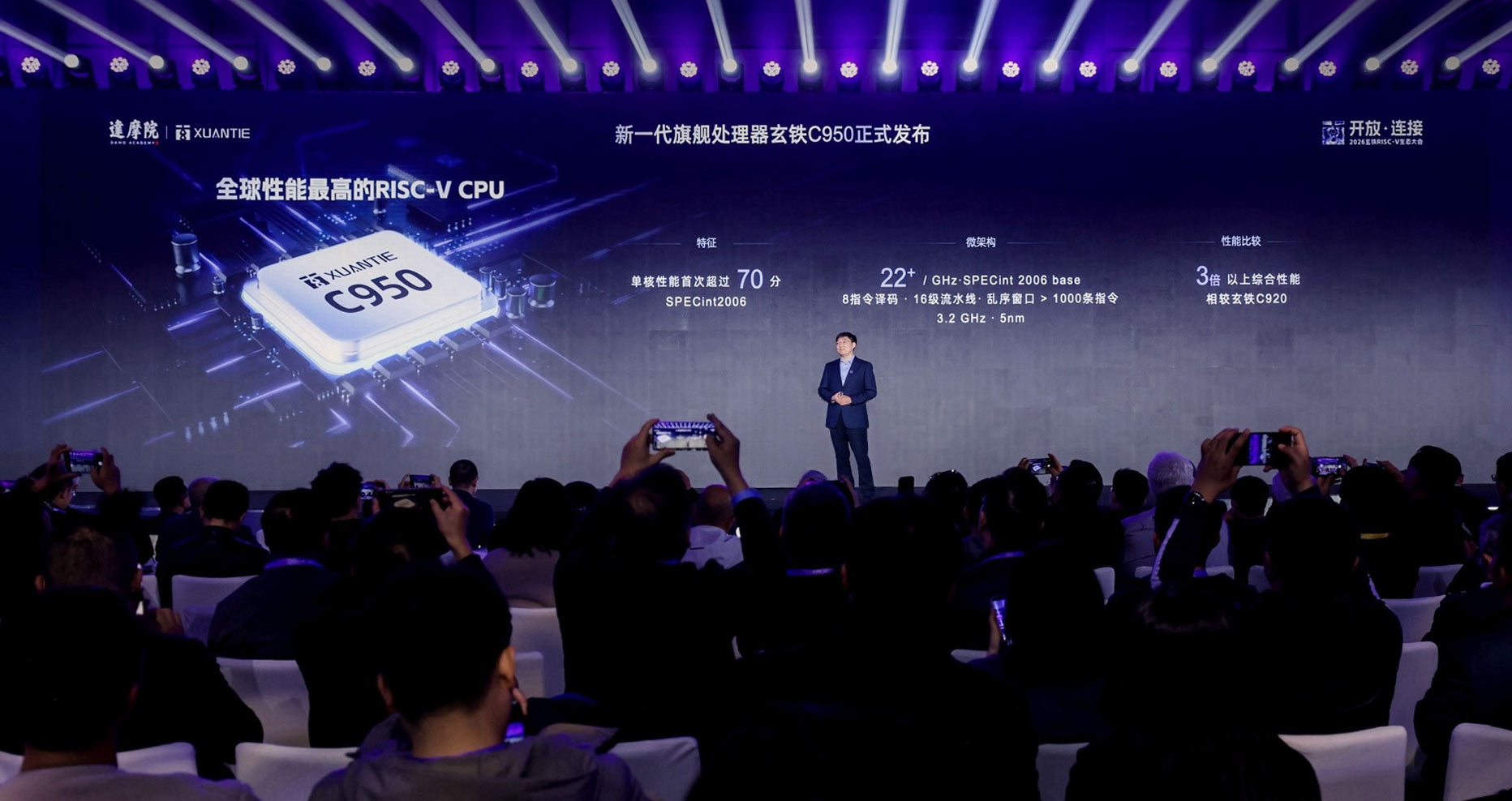

尽管各家有不同的主张和路径依赖,但近段时间已来已进入DPU产品的密集检验期,各大初创企业也在密集发布相关产品或方案来做市场的敲门砖。毕竟,作为主力芯片新物种,DPU的市场空间在快速扩张,预计至2025年全球市场有望达到245.3亿美元,复合增长率为51.73%。不止英伟达、英特尔等芯片巨头纷纷入局,国内则有数十家创业公司瞄准了DPU赛道,并在加速攻城略地。

而团队的网络经验是否深厚、软硬件打磨是否足够、生态的构建是否到位,都要将DPU拿到台面、走到场景中凭借实力说话,这是DPU厂商必然要直面的长久修行。

记者在第二届SmartNIC&DPU技术创新峰会现场看到,云脉芯联基于FPGA实现的DPU产品metaFusion-50在RDMA场景下的测试效果。工作人员介绍说,metaFusion-50拥塞控制实现机制可以迅速响应网络拥塞,通过硬件机制准确、及时降速,并确保带宽公平分配,同时可以及时、准确、全面的上报监控信息,可以满足算存分离、GPU内存共享以及AI模型训练等高价值场景的需求。

DPU正乘势而来,但如何破茧成蝶,需要认准趋势,按规律以科学的方法推进。无论如何,DPU的未来将殊途同归,业界共识是DPU一定会走定制化向通用化的路径。而谁能率先实现正反馈,谁就能将自己的“路径”变成行业公认的一大方向,这一步或仍需时间亦更需能力、实力和定力来检验。

(校对/张轶群)