集微网消息,8月25日,中国集成电路设计创新大会暨IC应用博览会(ICDIA 2022)在江苏无锡太湖国际博览中心正式开幕。

在下午举行的高峰论坛上,上海芯联芯智能科技有限公司(以下简称“芯联芯”)创始人暨董事长、源创芯动科技(宁波)有限公司创始人暨董事长何薇玲发表题为《创新应用-芯片IP化,IP芯片化》的演讲。

狄更斯说“这是最好的时代,也是最坏的时代”。何薇玲在演讲开始表示:“近两年半导体业历尽'世界的风云',正走进最好的时代。”同时,她也指出,每颗芯片从设计到量产再到上市热卖面临多重考验。每颗芯片的诞生带动的是背后900亿元的资产,同时需要依次迈过10-13个半衰期门槛。

其中,10-13个半导体产业半衰期门槛是最具挑战的部分,包括找资金、招人开工、MPW、nto、算法算力结合、产能、销售渠道等重重关卡,经过“MPW、nto、算法算力结合、产能”,IP芯片化大力提高成功率,但是点亮后热卖的芯片仅为十分之一。何薇玲会上指出,据业内统计,全球每100家芯片设计公司,应有一家可在先进工艺产品成功量产;国内芯片设计公司中一万家公司中仅有五家公司可量产(<12nm制程)。

何薇玲解释道:“对于半导体行业来讲,900亿元的资产投入离不开国家力量的支持,迈过10-13个半导体业半衰期,离不开芯片设计服务公司。”

面对挑战,诸多像芯联芯这样的芯片设计服务公司迎难而上,助力国内芯片设计公司顺利迈过“半衰期”,加速企业上市进程。

芯联芯成立于2018年12月,可以优化Fab流程中现有CPU内核效能、开发新CPU内核和衍生品、支持国内外客户所有先进技术活动及国际项目。其主要致力于CPU IP技术的创新型研发、ASIC定制的全流程IC设计服务(含Chiplet定制封装研发),使芯片设计公司得以使用安全,成熟且自主可控的技术,更快速便利地开发出SoC芯片。

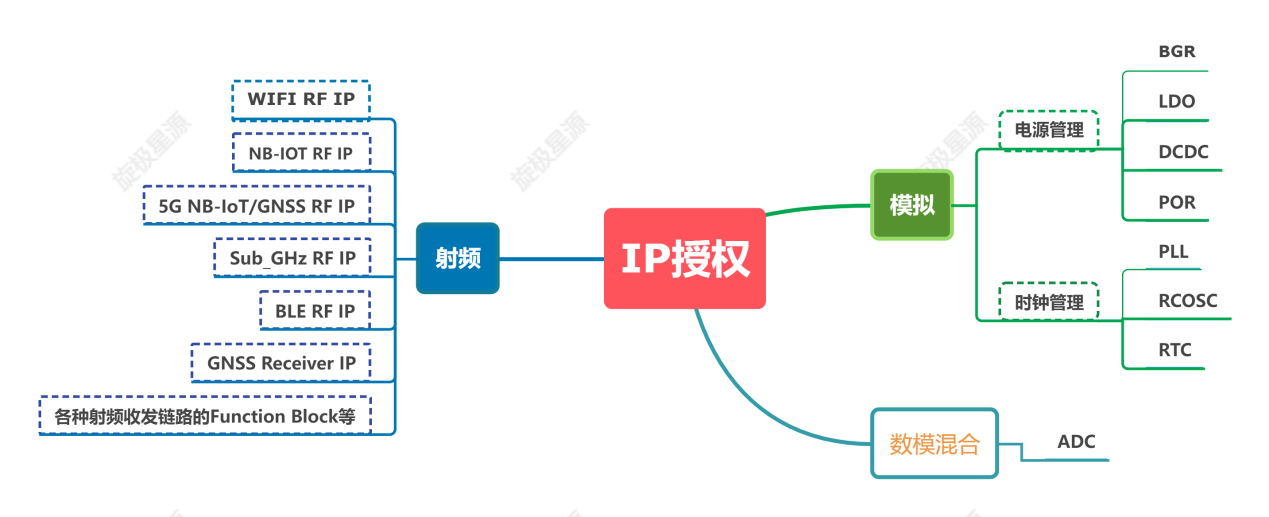

“当前,国内芯片设计公司要击败群雄,就需要走向国际舞台,提高良率,加速量产,迈向先进制程。”何薇玲表示,芯联芯作为芯片设计服务公司,投片工艺已涵盖成熟制程、先进制程(5nm\6nm\7nm),同中国万家芯片设计企业共同成长,正由芯片设计服务模式迈向Virtual IDM,并且提供芯片进化服务。

她进一步指出,Virtual IDM具备IDM的优点,避开其缺点,Virtual IDM在芯片制造、芯片封装、芯片测试环节采用战略合作模式;当前,单一工艺SoC无法达到最优化PPA与成本,SoC进化到异构3DIC正当其时。在芯片进化服务方面,芯联芯支持SoC进化到异构3DIC。

据悉,芯联芯已经获得国内外多家晶圆代工厂的产能保证,其中先进制程,如7纳米以下的制程能力将芯联芯带入国内芯片开发的头部服务公司行列,已经熟稔的和标准制程在上半年将有两颗CPU问世, 从台积电到新唐晶圆的设计服务,芯联芯将成为国内提供各个制程流片产能支持的首列。

一路走来,芯联芯助力芯片设计企业迈过重重关卡的同时,用户和市场对芯联芯的认可度日益增长,公司业务生态的成熟度不断提高,IP年出货量节节高升,研发布局持续加码。

2021年,芯联芯授权IP单年出货量已达1.7亿颗,2022年上半年授权芯片IP出货量达1.9亿颗。2022年下半年,公司将继续努力,力争在本年度的授权IP芯片出货量再创新高达到2.7亿颗。展望未来,芯联芯指出,在MIPS技术基础上,公司将致力于2025年单年冲击10亿颗IP授权生产出货量,为中国芯的自主可控和创新发展贡献力量。

此外,芯联芯在河南郑州的研发中心已经于2022年6月20日注册设立,于7月1日开始试运营。该中心除了开发优质高性能IP, 更将在高性能计算处理器工具软件和车规级处理器的研发和配套软件生态上继续发力,领先为用户和生态预作布局。(校对/刘沁宇)

登录

登录