日前半导体技术研究和调研机构Semiconductor Engineering(简称SE)讨论了芯片设计前沿正在发生的变化,以及支撑这些变化所需的条件。Synopsys Silicon Realization集团高级副总裁Bari Biswas、Cadence公司研发副总裁Michael Jackson、Microsoft Azure产品负责人Prashant Varshney、Rob Aitken(本小组的Arm研究员,现在是Synopsys的杰出架构师)和英特尔的高级首席工程师Mohamed Elmalaki参与了讨论。

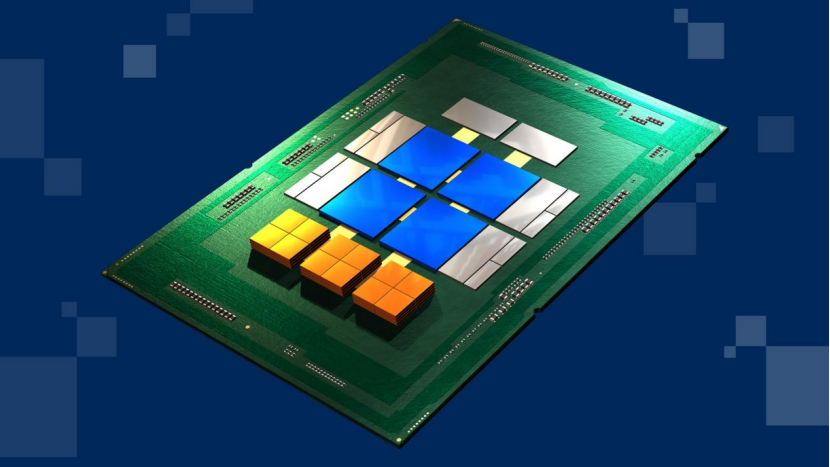

图源:Intel

SE:有关PPA的架构现在是个热点。封装非常重要,材料也很重要。我们看到芯片设计发生了根本性变化。为实现这一目标,对EDA工具有哪些要求,与今天有何不同?

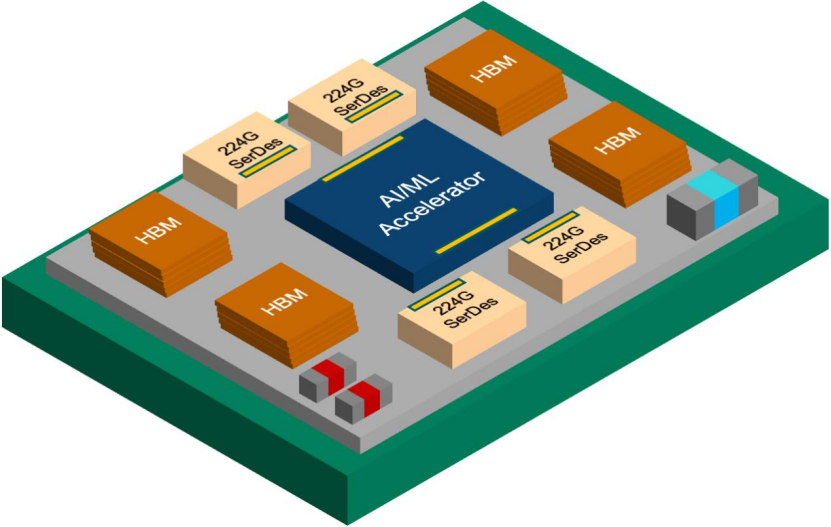

Biswas:芯片的未来是异构集成的。除了产品团队和设计公司完成的定制之外,许多设计正在前进到几纳米,这一进程的成本很高。IC设计本身正在变得多维——多芯片、多工艺技术节点,然后组装到一起。除了传统的IC设计人员之外,我们还看到更多来自系统背景的人在做这些类型的异构芯片。对于EDA公司来说,这既是挑战也是机遇。

挑战在于,需要从头开始考虑解决方案,确保系统设计人员的所有需求都要得到满足。从2D到3D,设计环境应该是无缝衔接的,它应该与2.5D和3D堆栈共享我们在2D空间中开发的一些基础设施和数据模型;允许在系统级别进行架构探索,并解决可扩展性问题。现在,我们可能正在谈论的是5-10个芯片,之后需要构建一个系统,允许扩展到数百个芯片,然后处理系统之间的连接。我们注意到最近出现了一些用于这些连接的协议或标准。这些是关键的挑战和要求。

Jackson:今天,2.5D和3D-IC的设计正在进行中,未来,我们将设计更复杂的产品。对于 EDA 解决方案,还需要实现一系列功能,这些功能将一直延伸到 2.5D 和 3D-IC 系统的物理实现。需要不同类型的分析,以及与包装和协同设计的连接;还需要为这些系统进行设计规划,之所以称之为系统是因为要将不同的芯片或小芯片组合在一起,然后能够进行多设计规划,处理诸如模具放置和凸块规划之类的事情。此外,还需要一个数据库。其中许多系统将是异构的,不仅在结构类型方面,它们可能具有RF传感器和数字,而且在所代表的过程技术方面也是如此。这些系统容量会很大,复杂性也在提升。

需要对功率、热度、3D静态时序、ECO进行高容量分析,然后进行到整个功能验证。其中大部分是现有功能的演变,增加了维度并能够处理复杂性。如今,这些设计主要由IDM完成,而且业界有一些举措正在促进小芯片的发展,这将需要一定程度的标准化。它类似于单芯片的标准化工作,但扩展到了多芯片配置。这将为一些公司打开大门,帮助它们为客户提供小芯片以进行整合。但除此之外,还牵扯到定制化芯片问题。

图源:SE

Lee:新工艺节点仍面临挑战,比如一个AI芯片的面积几乎等同于整个裸片的面积。现在,当考虑裸片集成多个芯片时,问题就会愈演愈烈,目前这种方法还处于早期阶段。我们有客户在做2.5D和3D,但这仅仅只是转变的起点。工具和方法是新的。它需要EDA公司和终端客户之间的密切合作。系统和芯片之间的界限逐渐变得模糊。以前,通过PCB上的多个芯片和多个封装获得异构能力。现在,我们能够将这些全部集成到一个封装中。所以,以前你有系统设计师帮助研究电磁学、系统或热完整性。而现在,所有这些分析都需要在多个芯片的背景下进行。挑战在于,传统的芯片设计人员习惯于EDA工作流程,但现在我们需要引入热分析团队和磁学分析团队。需要将新的方法、工具和物理特性引入到这个 3D-IC 工作流程中。这既是挑战,也是机遇。当我们三年后回顾过去时,就能够说,“现在我们对应该如何做到这一点有了更好的理解。”

SE:那么“云”在其中又可以发挥什么作用?

Varshney:如果倒退几年到2018年,台积电当时宣布了一个云联盟,并表示正在将5nm仿真转移到云端。这对行业来说证明了云可以提供安全性和性能,并激发了人们对云的发展动力和极大的兴趣。在2020年和2021年,人们正在尝试。他们说,这听起来很有趣,看起来很有希望。

他们现在已经完成了这项工作,从2021年年中到现在,他们开始研究如何迁移到云。变化悄然发生。目前,许多客户正在考虑三到五年的计划,以了解如何将所有内容迁移到云中。如果你正在研究5nm仿真或SoC,那么与16/14nm芯片相比,需要5到10倍的硬件资源才能做到这一点。有巨大的资源需求,并且应用到这些新节点,每个人都在努力想搞明白如何增加数据中心的容量,但这是不可能的。你必须创建新的数据中心,且无法再扩增容量。行业正处于这一抉择的风口浪尖。目前,EDA行业的云只有个位数,但正在迅速被采用。还有一些本地数据,这些数据必须在本地,但大量工作都将转移到云中。

SE:今天的工具箱中还欠缺什么?

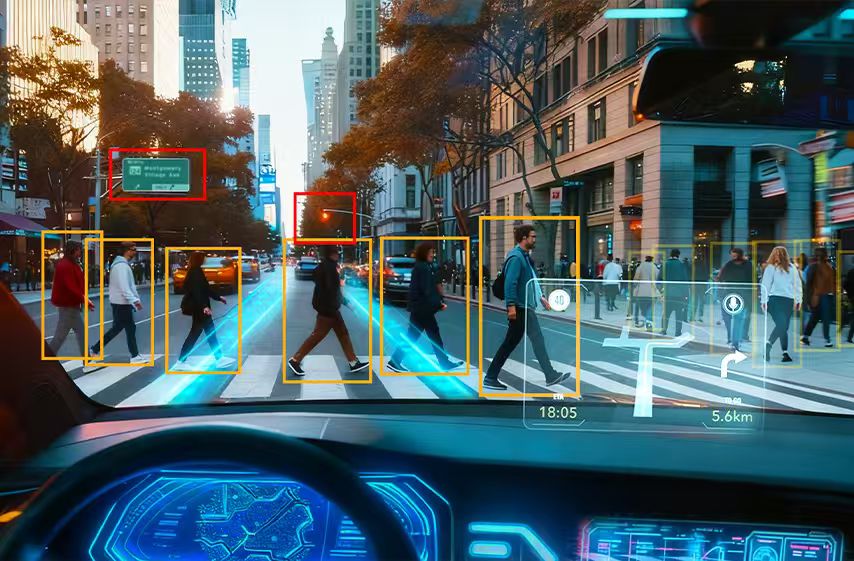

Elmalaki:我们没有看到工具箱里到底缺少什么的问题。但一些建模一直困扰我们,当然可以进行改进。我们的设计中,台积电或三星和英特尔的芯片都采用相同的封装。不同的公司有不同的小芯片组装封装解决方案,以及小芯片之间的接口,这带来了一些挑战。我们需要在压缩和数据传输方式方面进行创新。像时钟芯片和DFx这样的东西非常有帮助。CXL标准未来可期,已经投入大量使用应用。EDA部分并不是最具挑战性的,跨异构芯片运行的软件是整个行业最具挑战性的领域之一。在过去的两三年里,我们在如何将小芯片组装成封装方面已经走过了漫长的道路,在软件方面没有看到同样的改进。

SE:那么这些异构封装在未来会是什么样子呢?它们是标准IP的集合,半标准的“硬IP”,还是一切都是定制的?

Elmalaki:我们有很多用于 AI 工作负载的小型定制加速器。我们正在为其构建定制芯片,但随着代码的逐渐稳定,人们越来越不依赖固定功能,我们可能会看到向通用CPU和GPU的转变。你将拥有专用的和通用芯片,问题是你需要的侧重点是什么。(校对/Aaron)