芯片设计企业(Fabless)是近年来国内半导体产业增长最快的群体。行业数据显示,截止到2020年,中国的IC设计企业达到了2218家,比2019年的1780家多了438家,数量增长了24.6%。尽管在IC设计能力上,国内的力量正不断提升,甚至有些已与国际领先企业势均力敌,但从规模上看,大部分公司还处于小而弱的状态。此外,当涉及到数据分析、IT维护、导入量产方面,国内大部分IC设计企业与国外成熟公司相比则差距明显。

日前,普迪飞半导体中国区市场副总裁贾峻接受集微网专访时指出,在他们与十多家芯片设计企业交谈中发现,只有保持高良率,才能充分利用产能,实现更高的利润转化率。这对于当前产能紧缺的大环境,尤其关键。而大数据分析的挑战,成为IC设计企业面对良率提升问题时必须攻克的一关,越来越多的公司开始关注良率数据分析。

国内芯片设计企业快速成长中

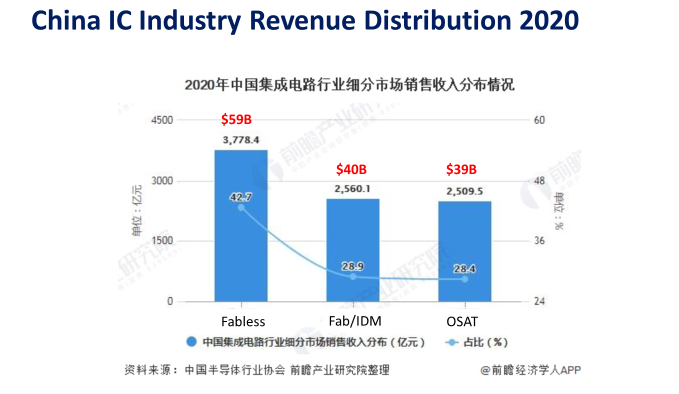

国内IC设计行业近几年来发展蓬勃。前瞻产业研究院的统计数据显示,2020年中国集成电路行业细分市场销售收入中:IC设计达590亿美元,远超晶圆制造(400亿美元)、封测(390亿美元);2015年-2020年,国内集成电路设计市场销售收入从1325亿元逐年增长到3778.4亿元,几乎翻三倍;2011年-2020年间,国内集成电路设计企业数量从534家逐年增长至2218家,翻了四倍。

但是如果和国外成熟厂商做一个对比,国内的IC设计产业规模相对还是较小。贾峻举例,仅英特尔一家2020年全年的收入(790亿美元)就超过了去年中国IC设计产业的总收入(590亿美元),高通2020的收入(235亿美元)相当于中国IC产业的一半。

不过,他也同时指出,高端芯片并不代表一切,从中低端芯片做起并非没有前途。“在美国同样也有大量企业专注在基于成熟工艺的半导体器件,如功率半导体。这些企业会把精力更多放在产品本身的设计上,诸如可靠性、降本增效等都是非常关键的因素,而先进工艺只是其中一个环节,企业要明确自身的策略,对产品目标要有清晰的认知,这也是一个不断积累经验的过程。”

Fabless更需要重视良率问题

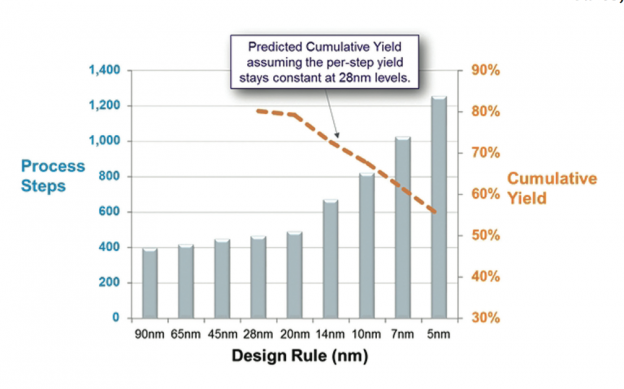

随着集成电路的不断发展,特征尺寸不断缩小,晶体管数量迅速增长,性能也在不断提升。与此同时,工艺难度急剧增加,成本不断上升。据Gartner统计,16nm/14nm芯片的平均IC设计成本约为8000万美元,设计7nm芯片则需要2.71亿美元。

高昂的成本问题注定良率被所有芯片厂商奉为圭臬。如何进一步提升良率,也是所有半导体产业链厂商挥之不去的终极问题。对于IC设计企业而言,接下去,在持续提升设计能力的同时,更要进一步打响提升良率之战。

贾峻指出,一方面,在产能紧缺的大背景下,芯片设计公司的试错机会减少,只有保持高良率,才能充分利用产能,实现更高的利润转化率。而更重要的一方面是,在半导体先进制程不断向前的当下,良率问题已经不单单是晶圆厂的技术能力问题。

随着工艺步骤的增加,如果每步良率保持在28nm水平,那么先进节点的预测累积良率将会下降。

资料来源:https://sst.semiconductor-digest.com/2016/02/yield-and-cost-challenges-at-16nm-and-beyond/

当半导体制程工艺下探到7nm、5nm时,工艺复杂度直线提升,很多缺陷都不在表面上,而是埋在里面,Fabless在做产品设计的时候就把监控结构埋在产品里面,通过特征数据的抓取及高效分析来快速准确地定位问题,从而提高产品良率。

此外,Fabless还会收集到来自封测厂以及制造厂的各种数据,要想保证产品质量或良率,就需要对这些数据进行分析,从而能够对产品设计进行反馈,把经验传承到下一代产品设计中去,进一步高效提升良率。

但是,在具体到数据分析层面时,国内很多年轻的Fabless还是会遇到许多实际操作的难题。

大数据挑战怎么破:良率管理系统能做什么?

据贾峻介绍,到了数据分析层面,缺乏有效的数据分析经验和手段是国内Fabless面临的困难。“拿到数据以后,哪些数据要整合对准?哪些分析能够帮助他们抓住问题?很多设计公司往往容易陷入迷茫。”

数据量巨大是一方面,同时,数据格式在不同工厂、甚至不同机台都会有区别,为了分析这些数据,工程师需要花费大量时间来对这些数据进行预处理与清洗。“在这个阶段,工程师需要花费80%的时间来对数据进行预处理,真正用于分析上的时间只有20%。”他说道。

贾峻进一步指出,处于不同发展阶段Fabless所使用的良率分析手段各有不同。初创企业对于数据分析的要求不高,通常会使用“Excel+画图软件”来处理数据,虽然入门门槛低,上手快,但缺点是一旦需要挖掘良率问题,数据清洗的工作就会呈指数级增长,使得数据分析工作耗时巨大,甚至不得不放弃一些分析。

数据规模不断增长的企业会转向采用脚本(R,Python等)来进行数据清理与制图分析,可以大幅减少数据清洗与统计时间,但其不具备数据库无法实现系统升级,且对员工个人编程能力要求较高,每次分析都需针对不同数据类型单独进行程序调试。

而如果想要实现更高效的良率管理,良率管理系统(Yield Management System,简称YMS)便开始进入一些Fabless的视野。

据了解,YMS是一种集数据管理、数据分析和专业工具于一体的系统,可在芯片设计、晶圆制造、封装测试等过程中收集数据进行分析,帮助工程师迅速找到提高良率的关键点。

对于半导体设计公司来说,YMS可以帮助工程师大幅提升数据分析效率,在同样时间内进行更大量、更高效的数据分析。其中关键环节就是数据库管理系统(DBMS),可以大大缩短工程师清洗、处理数据的时间。具体来看,经过一定的设置,数据库可以自动加载数据,并对数据自动进行预处理和对准,保证数据的正确、完整和有效。同时,YMS可以处理各种格式各个环节的半导体数据,并且允许做很多计算,可以快速得到摘要级别(summary level)的数据。

对于如何建立有效的良率数据分析平台,具体怎么选择合适的数据分析软件,贾峻的建议是,要结合公司所处的阶段看。“企业要对自身的情况有基本的概念,是开发新品尚未进入量产阶段,还是已经大批量生产,有大量的数据需要分析,亦或是工艺已经相当成熟,需要进行量产监控并了解影响良率的多方面因素等。”贾峻说,“企业要明确做什么样的分析,产生什么样的自动化报表,对于未来的新品要做哪些新的分析。”

集微网了解到,在半导体大数据分析领域深耕30余年的普迪飞半导体,一直与国际一流的流片厂及设计公司保持着密切合作,帮助先进 Fab、Fabless、IDM/System等国际领先的半导体公司完成了众多先进工艺量产提升项目。普迪飞也同样关注半导体初创公司和中小型企业的数据分析需求,针对不同成长阶段和规模的半导体企业,推出相应的数据分析模块以满足个性化的需求。

其中,基于云端的免费平台Exensio Fabless Quick Start,可满足中小型设计企业的基本需求。该系统由普迪飞进行维护,无需额外的硬件或资源,能够更有效地帮助处于起步阶段的芯片设计公司进行数据分析。对于较大规模的芯片设计公司而言,可以根据体量选择标准版或是大数据架构版本的Exensio平台,拥有更高的性能和更为灵活的功能,以便实现数据的深度追踪和挖掘。

除此之外,普迪飞不断在产品上拓展新的功能,如针对车用芯片市场所新推出的Exensio Test Analytics Lite。该产品在满足基本的数据分析能力的同时,提供了PAT,SBL/SYL等功能,可以根据AEC标准要求,高效地进行车规类分析。

“从普迪飞在中国大陆设立分支机构已有15年,与本土合作伙伴也积累了很长时间的合作经验,我相信今后5-10年,半导体仍是中国发展的重点产业,无论是政策还是资本都会继续向半导体产业倾斜,感受到中国半导体市场旺盛的需求,普迪飞也将以最有效的方式来支持中国本土的客户。”贾峻说。

登录

登录